用于GSM接收机的可编程分频器设计

2016-07-09陈勖房丽娜何春舅

陈勖, 房丽娜, 何春舅

(1. 深圳信息职业技术学院软件学院,广东 深圳 518172; 2. 北京大学深圳研究生院信息工程学院,广东 深圳 518055)

用于GSM接收机的可编程分频器设计

陈勖1, 房丽娜1, 何春舅2

(1. 深圳信息职业技术学院软件学院,广东 深圳 518172; 2. 北京大学深圳研究生院信息工程学院,广东 深圳 518055)

摘 要:可编程分频器是锁相环频率合成器中常见的电路之一。本文介绍了一种应用于GSM接收机频率合成器中的可编程分频器。整个电路由基于改进的单真相结构实现的4/5双模预分频电路和基于静态逻辑单元实现的可编程低速分频器组成,有效地降低了电路功耗,同时采用Σ-Δ调制技术来消除小数杂散。电路设计采用TSMC 0.18μmCMOS工艺实现。仿真结果表明电路可在GHz频率下正常工作,具有相位噪声低、功耗小等特点。在输入频率分别为800MHz和1GHz时,频偏10kHz处的相位噪声为-158.057dBc/Hz和-156.082dBc/Hz。电路整体消耗电流仅为1.5mA。

关键词:接收机,电荷泵锁相环,分频器

引言

现代社会中,各种无线通讯制式与人们的生活息息相关,人们也越来越依赖和享受移动网络和移动终端所带来的各种便利。但是对于便携式移动设备设计而言,高质量的产品离不开高稳定度的信号源。频率合成技术是目前用于产生高性能信号源的主流技术。频率合成器虽然只占到射频前端很小的部分,但是它的性能指标对于无线通信收发信机的选择性、灵敏度、信噪比、数据速率等关键指标有极大的影响[1-2]。

分频器是实现频率合成功能的重要模块,它的性能好坏对整个频率合成器有直接影响。分频器工作所消耗的功率占到了整个频率合成器功耗的很大部分,而且分频器的工作速度也极大地限制了频率合成器的工作速度。因此如何选择分频器结构以满足频率合成器的最高工作频率,是合成器在高频低功耗的条件下产生高精度信号的关键[2-3]。

GSM通讯系统相邻两个信道之间的间隔为200kHz[4],而整个收发信机选用的外部参考时钟频率为26MHz,为了完成信道间的正常切换,采用小数分频的频率综合器是不错的选择。

因此本文的目的就是为整个GSM系统射频收发信机的锁相环频率综合器设计一款实用的小数分频器,并采用Σ-Δ调制技术来消除小数杂散达到精确分频的目的。

1 设计原理

分频器的分频比可以是整数也可以是小数。对于整数频率合成器而言,输出频率为参考时钟的整数倍,输出频率的信道间隔等于参考频率。如果想要获得比较高的频率分辨率,就必须降低参考频率。这样,环路带宽会变小,环路的建立时间会延长。同时参考杂散也会出现在较低的偏移频率处。可见整数分频器的参考频率、环路稳定时间与分辨率三者之间存在相互制约的关系,而小数分频频率合成器在满足一定频率分辨率的条件下,可以选取更大的参考信号频率,这样既减少了环路锁定时间,环路带宽也相应变宽,同时又降低了对带内噪声的贡献。而且小数分频频率合成器的最小输出频率间隔是可以小于输入的参考频率的,更有利于信号在不同频道间的切换。但是小数分频会导致输出频谱中产生小数杂散影响到合成器的性能[2,5]。目前解决小数杂散问题的方法主要采用Σ-Δ调制方法,如图1所示。它可以将噪声从带内整形到带外的高频段后再通过频率合成器自身的闭环低通特性将其中的噪声滤除。另外,使用Σ-Δ调制器来控制分频比,它会产生一个仿随机比特序列去影响分频器瞬时的分频比,使分频器的结果为所需要的小数分频比。随着Σ-Δ调制器的输出不同,分频器的分频比也会动态变化[2,6]。

因此,本文将设计采用Σ-Δ调制的小数分频器。接下来首要任务是要分析频率综合器的工作频率范围。按照3GPP通信协议标准,GSM通信系统可以工作在四种模式下,即GSM850、E-GSM900、DCS1800、PCS1900[5]。根据各种模式的划分频段,可以确定压控振荡器的输出频率范围为[3296MHz,3980MHz]。由于分频器的输入就是压控振荡器的输出,而数控参考频率为26MHz,则可编程分频器的分频范围为[126.769,153.077],如果采用三阶Σ-Δ调制器来完成小数分频,调制器的输出范围为[-3,4],由于分频器工作时只能做整数分频处理,则得到实际的分频比为[123,158]。考虑到高达4GHz分频器设计的难度,在设计可编程分频器之前首先采用高速预分频器将压控振荡器的输入频率降下来,然后再进行多模分频处理使得设计相对简单。这里我们采用分频比为4的预分频器来进行降频处理,则确定最终的可编程分频器的分频范围为[28,43]。

图1 小数分频器结构示意图Fig.1 The diagram of Fractional-Ndivider structure

2 电路设计

在锁相环频率合成器电路中,应用最广泛的可编程分频器结构是吞脉冲结构(pulse swallowcounter,PSC)。吞脉冲分频器的分频比为PM+A,P为双模分频器的分频比,M为主分频器的分频比,A为辅助分频器的分频比。根据前述确定的分频比范围,分频器P采用高速4/5双模预分频器,M为7~10可编程分频器,A为0~3可编程分频器,从而正好匹配到整个可编程分频器的最小分频比为28,最大分频比为43。图2给出了本次设计的可编程分频器结构示意框图。

图2 可编程分频器结构示意图Fig.2 The diagram of programmable frequency divider

2.14/5双模预分频器

尽管已经对输入频率进行了降频,但是双模分频器的输入频率仍然高达1GHz,则静态逻辑不能胜任,而GSM系统对功耗和噪声有比较严格的要求,则模拟的SCL结构也不能胜任,因此动态真单相时钟结构TSPC(True Single-Phase Clocked)以较高的工作速度和较低的功耗成为比较合适的选择。

为了确保TSPC中的D触发器能够正常工作在1GHz左右的频率,对传统的TSPC结构进行改进,如图3所示。和传统的TSPC结构相比,时钟从远离电源轨线处换到了离电源轨线较近处,从而减少了内部节点寄生电容的影响,可以工作在更高的频率。改进后的结构因为对M2的源极寄生电容进行了预充电,所以其建立时间更短,当d为高电平时,由于M8预先导通,从而放电时间更短,减小了传播延时。当d为低电平时,则要求M5M6的放电速度要更快过M8M9,否则会出现功能错误。故M5M6的宽长比设计为M8M9的宽长比的2倍。

图3 改进的TSPC结构Fig.3 The improved TSPC structure

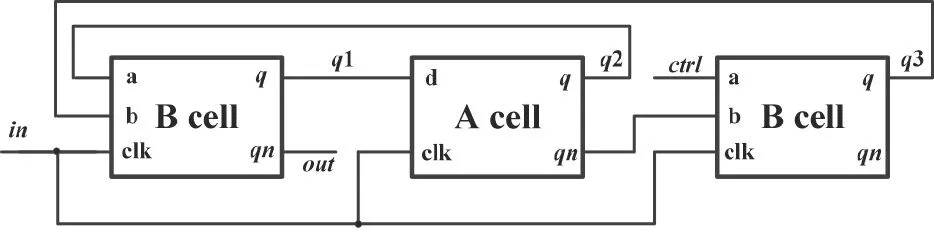

最终双模分频器的实现框图如图4所示。

图4 双模预分频器结构示意图Fig.4 The diagram of dual-modulus prescaler

从图中可以看到,顶层设计中包含自定义的A和B两个单元,单元A采用的是改进后的TSPC结构,单元B则是将与非门的功能嵌入到了改进后的TSPC结构中。值得注意的是,所有采用TSPC结构实现的寄存器都需要陡峭的时钟边沿,否则寄存器不能工作。

由图4中可以推导出三个级联单元的输出状态图为:000(初始态)→100→110→111→011→00 1→100→110→111→011→001→100…,其中000为初始态。正常工作后三个单元的输出将在状态100→110→111→011→001之间顺序循环,而000,010,101这三个状态因为前一周期输出真值的冲突而不可能出现。

2.2低速分频器M和A

接收机信道的选择是通过改变多模分频器的分频比实现的,根据分频比来确定吞咽计数器中M 和A的值。对于整数分频,只有在信道切换时才会改变分频比,信道确定后分频比不会发生变化。而小数分频的分频比在每个参考时钟周期都会实时变化,必须通过编程方式自动实现M和A的值。

根据前述设计原理,主分频器M需要通过编程控制完成7~10分频。

7分频的实现方式如图5所示,C单元是将与非门逻辑和寄存器的功能进行合并的基本单元。分频器主要由一个 2/3双模分频器和一个3分频器构成。3分频器的输出 q1q2以[10, 11, 01]循环,从而q2 的输出以011周期循环,qn2以周期100循环。利用qn2来控制前面的2/3双模分频器,即在一个qn2循环周期中完成一个3分频和两个2分频,那么一个完整的周期中分频比就是(3+2+2)*3/3=7,从而实现7分频的功能。

图5 7分频实现方式Fig.5 The diagram of 7 frequency divider

图6给出了8~10分频的核心电路,共使用了自定义的C、D、E三个单元。其中D是一个简单的静态逻辑实现的寄存器,E是一个静态寄存器实现的2分频电路。当控制信号ctrl为低电平时,实现8分频;当ctrl为高电平时,实现10分频;当ctrl由输出out信号来决定时,实现9分频功能。

图6 8~10分频实现方式Fig.6 The diagram of 8 to 10 frequency divider

辅助分频器A主要实现0~3分频的功能,结构相对简单,设计原理和8~10分频相类似,不再做重复的叙述。

3 仿真分析

整个可编程分频器的电路设计采用TSMC 0.18μm 1P5M的CMOS工艺实现。由于在整个可编程分频器中双模分频器的工作频率是最高的,因此版图设计需要着重考虑内部连线的优化以满足高频要求,而对于主分频器M和辅助分频器A的版图设计基本上以面积最小为优化原则。整个版图约为240*130μm2,如图7所示。

图7 可编程分频器版图Fig.7 The layout of programmable divider

对可编程分频器模块来讲,首先关心功能的正确性,同时必须满足 PVT的变化要求。其次是必须达到GSM接收机关于相位噪声的指标。仿真平台是建立在晶体管级电路设计和Verlog-A语言的基础上的。Σ-Δ的实现采用Verlog-A来描述。

Σ-Δ调制器的输出范围为[-3,4],分频器的分频范围为[28,43],为了保证仿真的完备性,需要进行多点仿真以覆盖分频器的分频范围。双模预分频器的输入范围为824MHz~995MHz,保留一定的设计裕量,选取输入频率为800MHz和1GHz。而小数分频器的整数部分选取31,36,39等值,小数部分设置则采用固定的177/520。

图8a)给出了在27℃典型情况下输入信号分别为频率1GHz时的仿真波形。此时Σ-Δ的整数部分为31。将图8a)中的波形内容汇总到表1中,可以看到有效计数时间为14.636μs,有效计数周期为467,从而计算得到平均分频周期为14.636/467=31.340471ns,分频比为31.340471ns/1ns=31.340471。仿真平台的编程数值为31+177/520=31.340384615,仿真和计算值之间的误差值为0.000086385。考虑到仿真时间的限制和数值精度的误差,误差的最大允许范围为[-3/467,4/467]=[-0.006424, 0.008565],则此时分频器工作正常。

图8b)给出了在27℃典型情况下输入信号分别为频率800MHz时的仿真波形。保持Σ-Δ的整数部分为31。波形数据如表1所示,计算得到分频比为39.174327ns/1.25ns= 31.339462,与实际的编程数值31.340384615的误差为-0.000922917,误差值落在误差允许范围[-0.006211, 0.008282]内,故分频器功能正确。

利用Cadence公司的SpectreRF对分频器进行稳态分析和噪声分析,可以得到在800MHz和1GHz时的相位噪声曲线,如图9所示。对于可编程分频器而言,比较关注的是偏差频率较小处的相位噪声,由图可见,输入信号为800MHz和1GHz时偏移频率10kHz处的相位噪声分别达到了-158.057dBc/Hz 和-156.082dBc/Hz,相位噪声结果表现良好。这应该要归功于低速分频器设计采用了静态逻辑,电路内部没有电流偏置和电压偏置的原因。

图8 可编程分频器输出波形Fig.8 The output waveform of programmable frequency divider

表1 波形数据分析Tab.1 The analysis of waveform data

图9 可编程分频器的相位噪声Fig.9 The phase noise of programmable frequency divider

4 结论

本文设计了一款应用于GSM无线接收机频率合成器中的可编程分频器。电路由基于改进的单真相结构实现的4/5双模预分频电路和基于静态逻辑单元实现的可编程低速分频器组成,能够有效地降低了电路功耗,提高电路的集成度。同时电路采用Σ-Δ调制技术来消除小数杂散。电路可实现28~43的连续分频比;在输入频率为800MHz和1GHz时,频偏10kHz处的相位噪声分别为-158.057dBc/Hz 和-156.082dBc/Hz。本电路完全满足GSM接收机频率合成器中可编程分频器的指标要求。

参考文献(References):

[1] RAZAVI B. RF Microelectronics[M]. NJ: Prentice Hall,1998

[2] 安娜. 基于锁相环分频器的研究[D]. 西安:西北大学,2014

AN Na. Study of frequency divider based on PLL Frequency Synthesizer[D]. Xi'an: Northwest University, 2014(in Chinese).

[3] 孙铁, 慧春. 一种CMOS高速可编程双模前置分频器[J].电子器件, 2005, 28(2): 398-401.

SUN Tie, HUI Chun. A CMOS High Speed Programmable Dual-Modulus Prescaler[J]. Chinese Journal of Electron Devices, 2005, 28(2): 398-401(in Chinese).

[4] GTS 05.10 V8.12.0. Digital cellular telecommunications system (Phase 2+); Radio subsystem synchronization (3GPP TS 05.10 version 8.12.0[S]. 1999

[5] 詹海挺.小数分频器的研究与设计[D]. 杭州:杭州电子科技大学,2012

ZHAN Haiting.Research and Design of Fractional Divider [D]. Hangzhou: Hangzhou Dianzi University, 2012(in Chinese).

[6] PENG Yu, ZHENG Gong, MING Gu, et al. A430MHz-2.15GHz Fractional-N Frequency Synthesizer for DVB and ABS-S Applications[C]. IEEECustom Integrated Circuits Conference (CICC),2009,1:247-250

【责任编辑:杨立衡】

【信息技术应用研究】

Design of programmable frequency dividerfor GSM receiver

CHEN Xu1, FANG Lina1, HE Chunjiu2

(1. Software Institute, Shenzhen Institute of Information Technology, Shenzhen 518172, China;2. Information Engineering Institute, Shenzhen Graduate School of Peking University, Shenzhen 518055, China)

Abstract:Programmable frequency divider is one of the common circuits in PLL frequency synthesizer. This paper introducesa programmable frequency divider used in the frequency synthesizer of GSM receiver. The whole circuit consists of a 4/5 dual-modulus prescaler which is implemented with the improved True Single-Phase Clocked (TSPC) structure and a programmable low-speed frequency divider which is based on the static logic cells, effectively reducing the power consumption of the circuit. The sigma-delta modulation technology is used to eliminate the fractional spur. The whole circuit used TSMC 0.18μm CMOS technology.The simulation results show that the circuit has an output phase noise of -158.057dBc/Hz@10kHz for 800MHz radio frequency input signal and -156.082dBc/ Hz@10kHz for 1GHz input signal, and it only consumes 1.5mA current.

Keywords:receiver; charge-pump phase-locked loop; Frequency divider

中图分类号:TN772

文献标识码:A

文章编号:1672-6332(2016)01-0043-05

[收稿日期]2015-12-20

[基金项目]深圳市科技计划项目(JCYJ20140418100633642)

[作者简介]陈勖 (1977-),男(汉),湖南邵阳人,博士后,高级工程师,主要研究方向:射频集成电路设计。E-mail:chen_xu@sziit.com.cn