去斜率信号的极坐标格式成像算法的FPGA实现

2016-05-14丁勇朱岱寅段化军石佳宁

丁勇 朱岱寅 段化军 石佳宁

摘 要: 针对机载合成孔径雷达(SAR)实时处理需求,传统的数字信号处理器(DSP)实现方式由于性能、功耗以及可靠性等原因,已经越来越不能满足实时性的要求,因此设计并实现了一种基于现场可编程门阵列(FPGA)的聚束SAR极坐标格式(PFA)算法,主要用于处理去斜率信号。该设计中采用两次Chirp?Scaling操作代替复杂的二维插值过程,提高了算法效率。由于雷达成像算法处理时常分为距离向、方位向分步实现,该次设计采用时分复用的方式,在处理时间无明显增加的情况下,极大的减少了FPGA的资源使用。该设计采用Xilinx公司KC705开发板进行验证,经测试当系统时钟频率工作在200 MHz时,处理单精度浮点8 192×8 192像素点SAR图像的时间约为8 s。

关键词: 合成孔径雷达; 去斜率信号; 极坐标格式算法; 现场可编程门阵列

中图分类号: TN953+.4?34 文献标识码: A 文章编号: 1004?373X(2016)09?0006?06

Abstract: Since the traditional DSP is unable to meet the real?time requirement due to the reasons of performance, power consumption and reliability, a FPGA?based polar format algorithm (PFA) for beaming airborne synthetic aperture radar (SAR) was designed and implemented to deal with the dechirp signal for the real?time processing demand of SAR. The twice Chirp?Scaling operation was used in this design to replace the complicated two?dimensional interpolation process to improve the efficiency of the algorithm. The step?by?step implementation of distance and azimuth directions is usually adopted in radar imaging algorithm. The way of time division multiplexing is adopted in this design to greatly reduce the resource usage of FPGA when a little processing time is increased. The design was verified on KC705 development board made by Xilinx. It approximately takes 8 s to process the SAR image of 8 192×8 192 single precision floating point pixels when the system clock frequency works at 200 MHz.

Keywords: synthetic aperture radar; dechirp signal; polar format algorithm; FPGA

0 引 言

合成孔径雷达能够全天候和全天时地获取高分辨率地面图像,在军事和民用领域都获得了广泛应用,已经成为现代雷达技术领域的重要发展方向[1]。聚束SAR通过调整波束指向长时间照射固定区域获得高分辨的图像,目前实时聚束SAR成像中应用最多的是极坐标格式算法(Polar Format Algorithm,PFA)[2?3]。PFA通过二维插值和二维快速傅里叶逆变换(IFFT)实现,处理过程较为简单,但是存在插值计算量大且精度不高的问题。基于Chirp?Z变换(CZT)的极坐标格式算法在方位向采用Chirp Z变换代替插值和方位压缩过程,因此,CZT能在减少方位向处理计算量的同时消除插值误差产生的影响[4?5]。但是基于CZT的方法在距离向仍需要插值处理。而基于Chirp Scaling原理(PCS)的极坐标格式算法能以两次FFT的代价实现距离向插值,同时在正侧视情况下,方位向也能用PCS代替插值,大大减小了计算量。由于整个算法由FFT和向量乘法运算构成,进一步提高了运算效率,更加有利于硬件实现。

去斜率信号脉压方式是针对线性调频信号提出的,对不同延迟时间信号进行脉冲压缩,在一些特殊场合,它不仅运算简单,并且还可以简化设备,降低采样速率,减小对存储单元的要求,已经广泛应用于SAR和ISAR中做脉冲压缩。对于去斜率信号处理也可以采用极坐标格式算法,在正侧视情况下,可以用PCS代替二维插值,大大地减少了计算量,节省处理时间。

实时数字信号处理的实现手段主要有DSP和FPGA。在SAR系统发展初期,DSP获得了广泛的应用。然而,随着SAR成像系统在性能、功耗以及可靠性等方面的要求不断提高,DSP已经越来越不能满足实时性的要求。而FPGA可以利用大规模的逻辑单元和片内存储器以及高速总线、流水处理等特有的硬件结构,快速完成FFT、复数乘法加法、CORDIC算法等数字信号处理基本运算。正是由于基于FPGA的信号处理系统具有极强的运算能力、丰富的可扩展性以及系统可重构等优点,因此特别适合数据率高、运算量极大的雷达成像信号处理系统[6?7]。

利用FPGA实现雷达信号处理时,选择的算法不同,处理效率与资源消耗都不一样。从效率上看,文献[8]利用插值方式对8 192×8 192大小的雷达信号进行二维插值处理,所需要时间约为20 s;而在文献[9]中,利用CS方式对4 096×4 096大小的雷达信号进行尺度变换处理,所需时间约为1 s。从资源上看,文献[8]采用时分复用的方式,距离向与方位向处理分时复用插值核,在处理8 192×8 192大小的回波数据时,开发平台KC705中的资源仍有很大的余量;而在文献[9]中,由于同时例化了多个FFT IP核,采用BRAM存储雷达参数,处理4 096×4 096大小的回波数据时,几乎耗尽了开发平台KC705中的部分资源。

在文献[8]和文献[9]的设计中,都不能有效的兼顾处理效率和资源消耗,而本文运用PCS的极坐标格式算法对去斜率信号进行处理,采用时分复用,雷达参数外存到DDR3等方式,并运用FPGA进行硬件实现,不但可以简化接收设备,减小内存的消耗,还可以提高运算效率,减少处理时间,因此特别适合雷达实时处理。

1 信号的算法处理流程

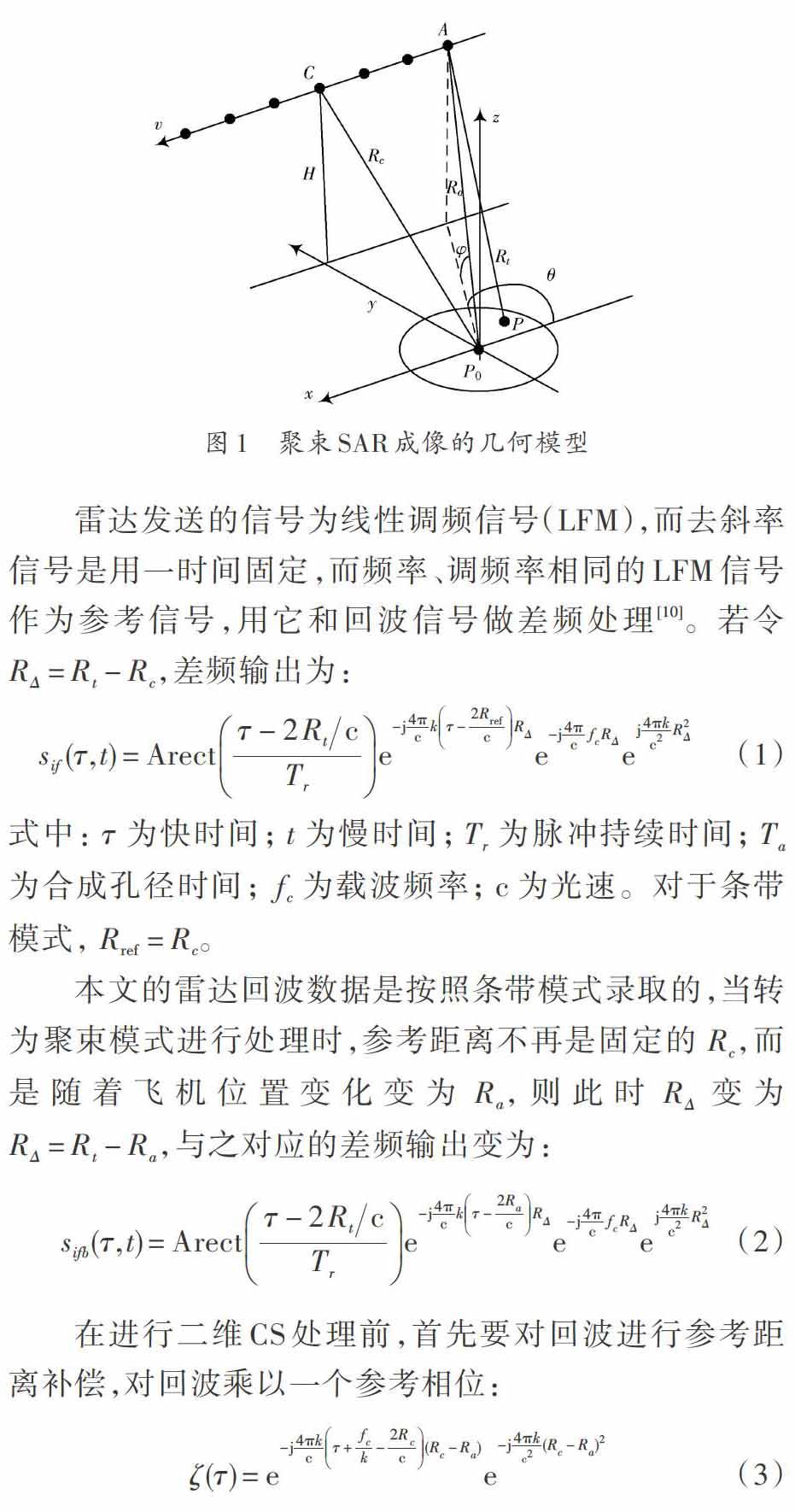

聚束SAR成像的几何模型如图1所示。

2 算法的FPGA系统框架

快速极坐标格式算法的FPGA处理系统包括以下几个模块:上位机、PCIe传输模块,数据选择模块,DDR控制模块,算法处理模块,如图3所示。

2.1 上位机

在数据处理之前,上位机负责把存储在电脑硬盘的数据发送到FPGA外带的DDR内存单元中,在数据处理结束以后,读取DDR内存单元中的数据到电脑硬盘中,处理显示。

2.2 PCIe传输模块

以Xilinx公司的PCIe IP为基础,结合DMA读取方式,在PCIe 2.0协议规范基础上,利用X4 lane通道可以实现120~500 MB/s的传输速度,快速地完成数据在电脑与内存单元之间的传输。

2.3 数据选择模块

数据选择模块负责PCIe传输模块与算法处理模块对DDR访问时,进行总线的裁决。

2.4 DDR控制模块

DDR控制模块主要完成以下两个功能:

(1) 按照算法需求,以Xilinx自带的IP核为基础,开发内存驱动程序,实现对内存单元的连续读写,跳跃转置读写等功能。

(2) DDR PHY:4 GB内存单元存储雷达参数与回波数据,在数据处理过程中实现数据的写入和读出。

在文献[9]中把雷达参数存储在FPGA的BRAM中,这样做有如下弊端:

(1) 占用BRAM资源:FPGA中的BRAM资源较少,雷达的参数很多,并且随着雷达处理数据的增大,BRAM占用量也会相应增加,如果参数存储占用太多的BRAM资源,会导致余下的BRAM资源不能满足算法处理的需求。

(2) 浪费时间:利用BRAM资源存储雷达参数时,首先要生成COE文件,然后再导入到BRAM中,当单个雷达参数的点数为8 192时,建立一个BRAM核需要5 min以上,当雷达参数达到10个时,仅建立BRAM核所需时间接近1 h。

(3) 可移植性差:当需要改变雷达处理数据大小或是修改雷达参数时,都需要重新生成BRAM核。

在本文中,由于4 GB的内存有很大的余量空间,提出了把雷达回波参数存储在DDR中的方法,上电时,从DDR中读取回波参数,送入到参数缓存模块,根据算法处理流程,从缓存模块中读取雷达参数用于计算。这样做有如下几个优点:

(1) 占用极少数的BRAM资源。由于雷达的算法处理一般是按照距离向处理,方位向处理这样的步骤进行分步处理时并不需要把所有的参数全部读取出来,每步读取的参数最多四个,因此在开辟的参数缓存模块只需要4个BRAM即可。在本系统中,需要存储的参数包括[x,y,z,tr,fr,ta,fa,]本系统中利用KC705 XC7K325T板卡实现,串行方式与并行方式对BRAM资源使用的对比见表1。

此处的串行方式是指本文中采用的时分复用方式,并行方式是指文献[9]中同时例化多个IP的算法实现方式。

(2) 节省时间。不再需要导入COE文件的过程,上电以后,直接把当前处理需要的参数导入到参数暂存模块即可,利用200 MHz时钟从DDR中读取7×8 192个参数所花时间为0.3 ms,在雷达处理过程中,可以忽略。

(3) 可移植性强。当改变雷达处理数据大小和参数时,只需要改变写入DDR的参数即可,不需要重新生成BRAM。

(4) 可扩展性强。雷达参数很多,放在FPGA中计算通常会耗费很多硬件资源,未来的研究架构是在上电时,把雷达参数放到Power PC中计算,计算完成后导入到FPGA参与算法计算,串行模式开辟的参数暂存模块正好可以存储计算完成的雷达参数。

2.5 算法处理模块

算法处理模块分为以下四个步骤,如图4所示。

2.5.1 补偿处理

雷达数据的录取通常按照条带模式采样,但是在进行雷达回波处理时,为了获得较高的方位向分辨率,一般采用聚束模式进行处理,对于去斜率信号,从条带模式到聚束模式有一个参考距离的补偿。补偿模块就是完成条带模式到聚束模式的参考距离补偿。在实际的雷达处理中,由于补偿处理是针对距离向进行的,因此可以把补偿模块与距离向处理合并到一起进行处理。

2.5.2 距离向处理

距离向运用PCS原理,按照图5(a)的流程框图完成处理步骤后,送入到方位向处理模块进行处理。

2.5.3 方位向处理

方位向处理也是运用PCS原理,按照图5(b)的流程框图进行处理后,送入到后面做距离向FFT处理。

2.5.4 距离向FFT处理

对距离向做完FFT以后,对数据取模计算,即可得到雷达图像。

在雷达数据处理过程中,需要大量使用FFT,并行实现方式是同时例化多个FFT IP核,雷达信号处理通常按照距离向处理,方位向处理的流程分步进行,同时例化多个FFT IP核可以简化代码设计,但是却极大地占用了FPGA的资源。在本系统中,只需要例化一个FFT IP核,采用时分复用的方式,较并行方式而言,增加的处理时间极小。在本系统中,如果采取并行设计方式,做7次FFT运算就需要例化7个FFT IP核,本系统中利用KC705 XC7K325T板卡实现,表2是两种设计方式的资源比较。

3 实验处理结果与分析

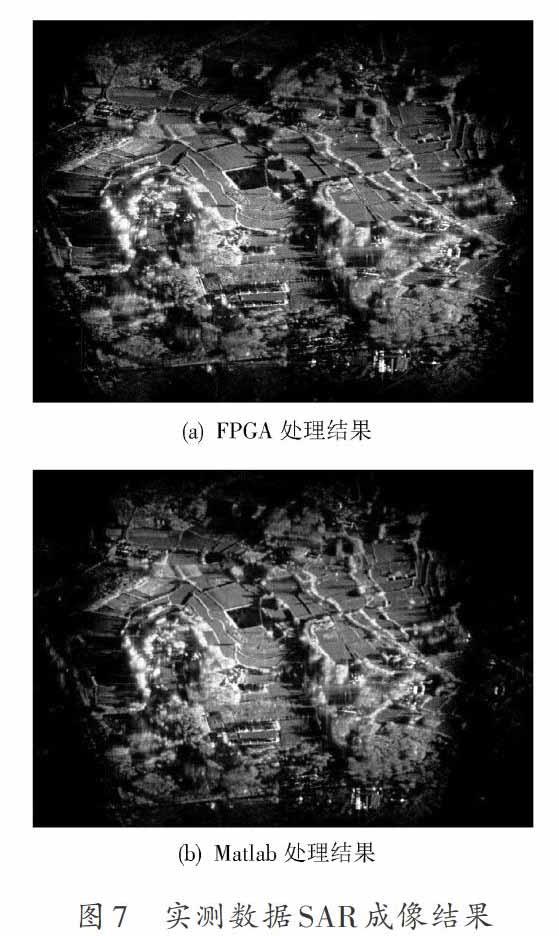

本算法处理系统中采用Xilinx公司的KC705开发板来验证极坐标格式算法处理的可行性。为了验证FPGA片内算法处理的效率与效果,系统通过PCIe接口连接上位机与KC705板卡,实现SAR回波数据的发送与接收。外部输入200 MHz高精度的差分时钟以驱动FPGA片内各模块。FPGA的通用I/O口连接LED来监测片内处理各步骤的工作状况,提供用户复位按键对FPGA进行全局复位。

本处理系统主要是处理正侧视的去斜率信号,表3是实测数据的部分雷达参数。

表4是系统处理8 192×8 192个像素点实测数据的FPGA使用情况。系统利用片内DSP48E1资源来提高乘加模块,FFT模块的处理速度。BRAM18E1存储资源使用量较低,增强了对大数据量处理的缓存FIFO的拓展性。最核心的LUT资源利用率较高,用于实现对FPGA的逻辑处理与流程控制。

4 结 论

本文从提高SAR成像效率出发,设计并实现了机载条带SAR在正侧视情况下去斜率信号的极坐标格式算法。为了让系统更高效,本文选取了基于PCS的极坐标格式算法以2次FFT的代价代替插值,提高了算法效率和精度;提出了一种利用DDR存储雷达参数,初始化时开辟缓存的方式来节省FPGA资源使用的方案;设计了一种在不降低雷达处理效率的前提下,利用时分复用FFT IP核的方式极大地节省了FPGA片内的BRAM与DSP48E1资源。本算法处理系统利用Xilinx公司的Kintex?7 FPGA开发板作为硬件开发平台,用PCIe接口实现数据传输。经实验统计,本系统处理8 192×8 192条带去斜率SAR图像需要约8 s时间,成像效果与使用Matlab处理相当。由于采用基于PCS的极坐标格式算法只能处理正侧视的数据,当引入斜视角的时候,方位向采用CS的处理方式已经不再适用。如果要针对任意斜视角输入下的去斜率信号进行处理,可以利用尺度变换处理距离向,利用插值处理方位向。

参考文献

[1] 郑晓双,禹卫东,李早社.机载SAR实时运动补偿和成像的FPGA实现[J].数据采集与处理,2008,23(5):614?618.

[2] 周芳,唐禹,张佳佳.机载高分辨聚束式SAR实时成像处理系统的FPGA实现[J].电子与信息学报,2011,12(5):1248?1252.

[3] 毛新华.PFA在SAR超高分辨率成像和SAR/GMTI中的应用研究[D].南京:南京航空航天大学,2009.

[4] 孙进平,袁运能,王俊.CZT在聚束SAR极坐标格式成像算法中的应用[J].系统工程与电子技术,2002,24(10):4?7.

[5] BURNS B L, CORDARO J T. A SAR image?formation algorithm that compensates for the spatially?variant effects of antenna motion [J]. SPIE proceedings, 1994, 2230: 14?25.

[6] 谢宜壮,龙腾.基于FPGA的SAR信号存储与预处理模块设计与实现[J].信号处理,2010,26(2):180?183.

[7] 熊君君,王贞松,姚建平.星载SAR实时成像处理器的FPGA实现[J].电子学报,2005,33(6):1070?1072.

[8] 毛莹,张近东,张弓.完备单精度SINC插值的FPGA实现[C]//第十三届全国雷达学术年会论文集.西安:中国电子学会,2014:668?671.

[9] ZOU Linchen, ZHANG Jindong, ZHU Daiyin. FPGA implementation of polar format algorithm for airborne spotlight SAR processing [C]// Proceedings of 2013 11th IEEE International Conference on Dependable, Autonomic and Secure Computing. Chengdu, China: IEEE, 2013: 143?147.

[10] 保铮,邢孟道,王彤.雷达成像技术[M].北京:电子工业出版社,2005.

[11] ZHU D, YE S, ZHU Z. Polar format algorithm using chirp scaling for spotlight SAR imaging formulation [J]. IEEE transactions on aerospace and electronic systems, 2008, 44(4): 1433?1448.