基于VxWorks与PowerPC的雷达信号分选系统设计

2016-01-23韩卫国陆广驰9404部队河北秦皇岛06600中国船舶重工集团公司第七二四研究所南京53

韩卫国,朱 润,陆广驰(.9404部队,河北秦皇岛06600;.中国船舶重工集团公司第七二四研究所,南京53)

基于VxWorks与PowerPC的雷达信号分选系统设计

韩卫国1,朱润2,陆广驰2

(1.91404部队,河北秦皇岛066001;2.中国船舶重工集团公司第七二四研究所,南京211153)

摘要:针对当前密集复杂的电磁环境下雷达信号分选实时性与有效性问题,介绍了一种雷达信号分选系统设计。该系统基于实时操作系统VxWorks与高性能PowerPC处理器的组合平台,并采用了一种密集电磁环境下的自适应信号分选算法。通过合理分配任务结合相适应的任务间和CPU间通信方式,使得整个算法流程能够在四片PowerPC上有序高效地运行,从而在平台与算法两方面保证雷达信号分选的实时性与有效性。

关键词:VxWorks; PowerPC;雷达信号分选

0 引言

随着雷达技术与通信技术的飞速发展,在现代战场环境下,空间电磁环境空前复杂、密集,这对电子侦察的手段与性能都提出了更高的要求[1]。作为电子侦察的重要环节——雷达信号分选处理的数据量愈加庞大,任务愈加繁重,算法愈加复杂。通常采用的高速DSP由于算法设计难度较高,软件继承性较差,已越来越难以应对这些复杂的问题。一种基于新体制通用处理平台的雷达信号分选系统便成为了迫切需求。

1 VxWorks与PowerPC简介

采用“高性能通用处理器+实时操作系统”组合的平台具有运算速度快、实时性高、算法设计灵活、软件可移植性与可继承性强等特点,能够较好地满足现代雷达信号分选的需求。

1.1实时操作系统VxWorks

VxWorks操作系统是风河公司设计开发的一种嵌入式实时操作系统(RTOS)。VxWorks操作系统主要有如下特点:

·实时性:通过极短的任务间切换时间(微秒级)与高效的多任务控制机制(优先级抢占调度与轮转调度),充分保证了系统的实时性要求。

·多任务:由于外部事件的异步性,VxWorks允许对各个外部事件建立多个任务来执行。系统通过给这些任务分配CPU时间来获得并发性。

·可剪裁性:开发者可以根据自己的需要对Vx-Works操作系统的功能与大小进行增减,从而能够保留更多的系统资源用于应用程序。在某些应用中,Vx-Works可能只有几十KB的大小。

·可靠性:稳定、可靠一直是VxWorks的一个突出优点。自从对中国的销售解禁以来,VxWorks以其良好的可靠性在中国赢得了越来越多的用户。

1.2高性能PowerPC处理器

PowerPC通常指的是使用PowerPC指令集的处理器。随着PowerPC的发展,其在性能、集成度、功耗等优势方面不断得到突破,使用PowerPC架构的处理器已经在通信、工控、国防军工领域得到了广泛的应用。本系统采用的VPX6-Q8640D处理板包含了四片Freescale公司的先进双核处理器MPC8640D。该处理器具

有如下特点[2]:

·双核处理器:处理器工作主频1.0 GHz,具有两个e600内核,支持对称多处理器(SMP)工作模式,便于组成多处理器并行处理系统;

·集成度高:内部集成DDR2内存控制器、I2C控制器、可编程中断控制器(PIC)、以太网控制器等多种设备,支持4x Serial RapidIO与8x PCI Express两种高速通信接口标准;

·矢量浮点运算能力强:支持AlteVec矢量处理技术,具有32GFLOPS的最高处理能力;

·功耗较低:典型功耗为14 W,相比x86架构的CPU具有更好的性能/功耗比;

2 雷达信号分选流程

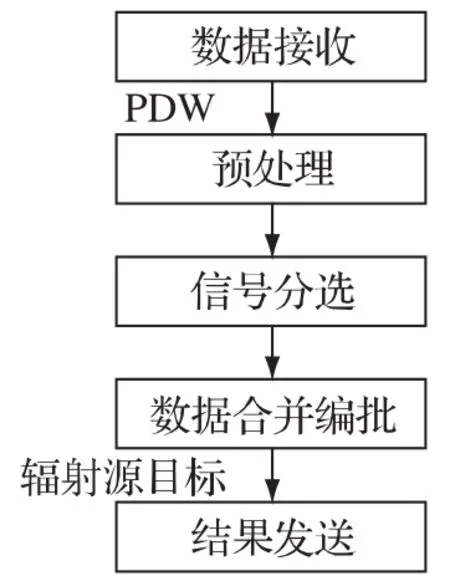

整个系统信号分选的流程如图1所示。

图1 信号分选流程

数据接收部分主要接收前端送来的数据包,对数据包进行校验、解包,完成PDW(脉冲描述字)格式转换。

预处理部分主要利用AOA(脉冲到达角)、CF(载频)、PW(脉宽)等进行聚类,对脉冲流密度进行稀释,从而降低后面信号分选的计算压力。

信号分选常见的算法有累积差直方图法(CDIF)[3]、序列差直方图法(SDIF)[4]。这两种算法不具备二次及高次谐波的抑制能力。Nelson提出的PRI变换法[5]加入了相位因子,能够较好地实现对高次谐波的抑制,同时也较大地增加了算法计算的复杂度。综合考虑雷达信号分选的实时性与有效性,本系统采用了一种密集电磁环境下的自适应信号分选算法[6]。该算法基于PRI变换法,可以根据脉冲流密度自适应地调整信号分选算法处理的相关参数,将信号分割为高、低重频分别进行分选,较好地解决了密集电磁环境下的信号分选问题[6]。

数据合并编批部分主要完成周期内信号分选结果合并、虚假结果抑制、周期间分选结果关联、方位滤波、分选结果编批等工作。

结果发送部分根据后端的需求格式将结果进行打包,按约定的通信方式发送结果。

3 信号分选在VxWorks与PowerPC平台上的实现

本次选用的VPX6-Q8640D处理板包含了四片PowerPC处理器,信号分选在该平台上的实现主要会涉及到三个方面:信号分选在四片CPU上的任务分配、同一个CPU上各任务之间的通信、不同CPU之间的通信。

3.1信号分选在各CPU上的任务分配

雷达信号分选在四片CPU上的任务分配采用了串行与并行处理相结合的方法。根据仿真测算,在信号分选整个流程中,系统的主要资源消耗集中于信号分选部分,故在四片CPU中分配两片用于信号分选算法的并行处理,剩余两片分别用于信号预处理与分选结果合并编批,这两部分与信号分选算法形成了串行处理。任务分配如图2所示。

CPU1接收到前端送来的PDW数据后进行解包、预处理。在完成预处理后发送PDW给CPU2与CPU3之前需轮询两个CPU当前的状态,若其中任何一个处于空闲,则将PDW发送给此CPU进行分选操作。CPU2与CPU3分选结束将完成信息反馈给CPU1,将自己置为空闲状态,同时将结果发送给CPU4进行数据合并编批,并将完成编批的结果发送出去。

图2 任务的分配

3.2 CPU内任务间的通信

在同一个CPU内不同任务间存在相互通信的情况,如图2中CPU1内PDW接收与预处理两个不同任务都需要访问PDW缓存。对与此情况VxWorks操作系统提供了丰富的任务间通信机制,用于协调多个独立任务间的活动。任务间的通信方式主要有如下几种方式:

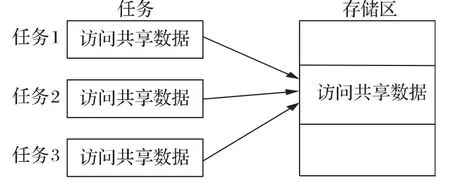

(1)共享内存:任务间最常用的通信方式。操作系统中所有的任务都处于同一个线性地址空间中,所以通过共享内存来共享数据比较容易实现。

图3 共享内存

(2)信号量:在VxWorks操作系统中,该通信方式被高度优化,并提供了最快的任务间通信机制,用于实现资源互斥与任务同步。

(3)消息队列:可以有多个任务读写,交换信息的基本单位为消息,允许多个不同长度的消息排列在缓冲器中。

本系统设计主要采用了共享内存和信号量两种通信相结合的方式。共享内存主要用于任务间传递数据,但由于可能出现多个任务同时访问该内存导致某个任务读取内存数据的同时内存数据被另一个任务改写,从而发生错误。为避免任务间的竞争,采用二进制信号量能有效地对共享内存的访问进行互锁。图2中CPU1中PDW接收与预处理两个不同任务访问PDW缓存的流程如图4所示。

图4 PDW接收与预分选任务通信流程

3.3 CPU之间的通信

在使用多CPU进行数据处理时,CPU之间的数据传输与同步需要CPU之间可以进行通信。VPX6-Q8640D处理板CPU之间的通信方式主要有网络、PCIE、Serial RapidIO(SRIO)等。本系统选用SRIO方式来实现CPU之间的互联通信。每个CPU通过板上SRIO SWITCH与其他CPU进行互连,每个CPU有一个×4的3.125Gbps SRIO串行总线接口,提供双向1.25GB/s的发送和接收数据带宽连接到板上SRIO SWITCH。由于SRIO交换机是非阻塞机制的,多个数据传输可以在同一时间并发。例如,CPUA可以传输数据到CPUB,同一时间CPUB可以发送数据到CPUD。

本系统CPU之间使用SRIO方式进行通信的主要流程如图5所示。

图5 CPU之间SRIO通信方式

在通信开始前,发送CPU与接收CPU需分别初始化自己的发送、接收窗口,将自己的内存窗口地址映射到通信总线。发送CPU通过DMA方式将数据发送到总线地址,此时由于接收CPU已将自己的内存地址映射到总线上,通信的数据相当于直接写入了接收CPU内存中。在发送完数据后,发送CPU向接收CPU

发送门铃,通知其数据已传输完毕。接收CPU收到门铃后产生中断,获取门铃号,通过门铃号从内存中读取数据,并执行与门铃号相对应的操作。

4 结束语

随着通用处理器技术的飞速发展,基于高性能通用处理器和实时操作系统的雷达信号处理平台将更富竞争力。相比DSP专用处理器,该平台能够在操作系统支持下既能保证实时性,又能增加软件设计的灵活性,缩短开发周期,降低后期维护成本。此外在较为复杂的多任务程序设计时,进行合理的任务分配、任务间与CPU间通信机制的选择对整个系统的稳定性、可靠性有着至关重要的作用。此雷达信号分选系统在某型号雷达中得到具体应用,经过长时间验证运行稳定,可靠,取得了良好的效果,对基于VxWorks与PowerPC平台的系统设计具有借鉴作用。

参考文献:

[1]王文光,常伟光,王俊.对基于PRI谱计算脉冲重复间隔的一种改进方法[J].雷达与对抗,2006(4):22-24.

[2]Freescale Semiconductor Inc.MPC8640 and MPC8640D Integrated Host Processor Hardware Specifications[M].America: Freescale Semiconductor Inc,2014.

[3]Mardia H K.New Techniques for the Deinterleaving of Repetitive Sequences[J].IEE Proceedings,1989,136(4):149-154.

[4]Milpjevic D J,Popovic B M.Improved Algorithm for the Deinterleaving of Radar Pulse[J].IEE Proceedings,1992,139(1):98-104.

[5]Nelson,D J.Special purpose correlation functions for improved signal detection and parameter estimation[C].In Proceedings of International Conference on Acostics,Speech,and Signal Processing(ICASSP’93),1993.4:73-86.

[6]苏彦华,胡进.一种密集电磁环境下的自适应雷达信号分选算法[J].雷达与对抗,2012,32(3): 12-15.

Design of radar signal sorting system based on VxWorks and PowerPC

HAN Wei-guo1,ZHU Run2,LU Guang-chi2

(1.Unit 91404 of the PLA,Qinhuangdao 066001,China; 2.No.724 Research Institute of CSIC,Nanjing 211153)

Abstract:In view of the real-time and effectiveness problems of radar signal sorting under the dense and complex electromagnetic environment,a radar signal sorting system is designed.Based on the combined platform of the VxWorks real-time operating system and the PowerPC high-performance processor,the system adopts an adaptive signal sorting algorithm in the high-electromagnetic-density environment.Reasonable task allocation combined with the suitable communication modes between the tasks and the CPUs is used to make the whole process of the algorithm run orderly and efficiently on four PowerPCs.Therefore,the real-time performance and effectiveness of radar signal sorting are achieved in both the platform and the algorithm.

Keywords:VxWorks; PowerPC; radar signal sorting

作者简介:韩卫国(1965-),男,高级工程师,研究方向:雷达试验与测量技术;朱润(1984-),男,工程师,硕士,研究方向:雷达数据处理;陆广驰(1982-),男,工程师,硕士,研究方向:雷达数据处理。

收稿日期:2014-12-19;修回日期:2015-01-05

文章编号:1009-0401(2015)01-0021-03

文献标志码:A

中图分类号:TN911.7