基于FPGA的数字频率计设计

2015-12-08周嘉腾胡佳文

周嘉腾+++胡佳文

摘 要:利用FPGA的等精度测量原理设计数字频率计,可实现1HZ-100MHZ信号频率的等精度频率测量并增加测量周期、时间间隔,占空比的功能。本设计以Altera FPGA系列DE0-Nano Cyclone IV器件为核心,运用VHDL语言设计功能模块,进行信号的控制、数据读取、运算处理以及屏幕显示。实验表明:该频率计具有测量精度高、功能丰富、控制灵活等特点。

关键词:等精度测量 FPGA 电压比较器

随着微电子技术和计算机技术的发展,可编程逻辑器件,EDA技术,SOPC等新概念和新技术层数不穷新技术的应用迅速渗透到电子,通信,信息汽车制造等领域,有力的推动了社会生产力的发展和社会信息化程度的提高。在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案和结果都有密切的关系,因此,频率的测量方法的研究越来越受到重视。基于传统测频原理的频率计的测量精度随被测信号频率的下降而降低,在实用中有较大的局限性,而FPGA等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测量精度。

理论分析

1、低频信号测量

低频信号一般采用间接测频法。通过测量待测信号的周期并求其倒数,需要有标准频率的信号,在待测信号的一个周期内,记录标准频率的周期数,这种方法的计数值会产生±1个脉冲误差,并且测试精度与计数器中记录的数值有关,为了保证测试精度,测周期法只适用于低频信号的测量。

2、高频信号测量

高频信号采用直接测频法。直接测频法就是在确定的闸门时间内,记录被测信号的脉冲个数。由于闸门时间通常不是待测信号的整数倍,这种方法的计数值也会产生最大为±1个脉冲误差。进一步分析测量准确度:待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量准确度为&=Tx/T=1/Fx。由此可知,直接测频法的测量准确度与信号的频率有关:当待测信号频率较高时,测量精确度也较高,反之测量准确度较低。因此直接测频法只适合测量频率较高的信号,不能满足在整个测量频段内的测量精度保持不变的要求。

3、等精度测量

等精度测频的方法是实在直接测频方法的基础上发展起来的,他的闸门时间不是固定的值,而是被测信号的整数倍,即与被测信号同步,因此避免了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。在测量过程中,有两个计数器分别对标准信号和被测信号同时计数,首先开启闸门开启信号(预设闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才开始真正计数,然后预设闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次侧量过程。

采用等精度频率测量法,测量精度保持恒定,不随所测信号的变化而变化。在快速测量的要求下,要保证较高精度的测频,必须采用较高的标准频率的信号。单片机受本身时钟频率和若干指令运算的限制,测频速度较慢,无法满足高速高精度的测频要求;而采用高集成度、高速的现场可编程门阵列FPGA为实现高速、高精度的测频提供了保证。

系统设计

1、电路设计

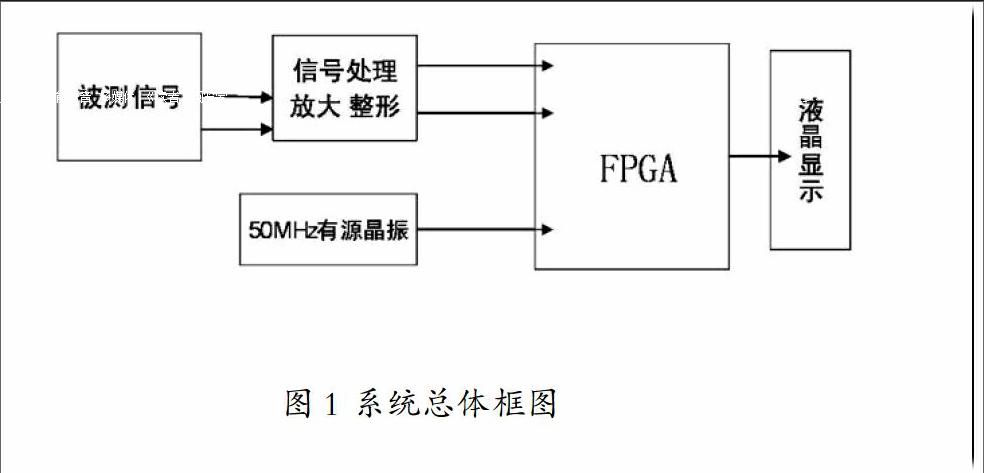

系统总体框图如图1所示。

图1 系统总体框图

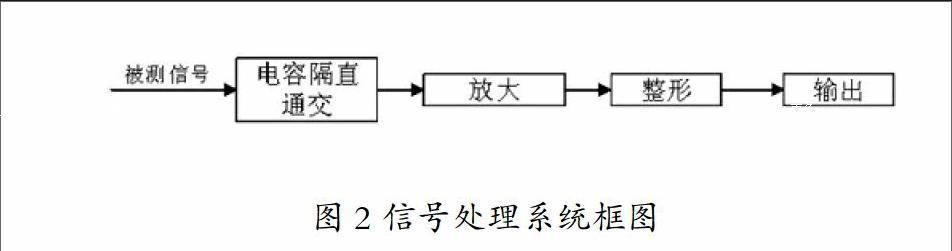

信号处理系统如图2所示。

图2 信号处理系统框图

1.1放大电路

运算放大器是集成器件,集成电路中大量使用有源器件组成的有源负载,以获得大电阻,提高放大电路的放大倍数;将其组成电流源,以获得稳定的偏置电流,所以一般集成运放的放大倍数与分立元件的放大倍数相比大得多,而且其相对精度好,故对称性能好,特别适宜制作对称性要求高的电路。低噪声高速运算放大器OPA842使用统一,两个内部增益稳定,电压反馈架构增益级,实现了非常低的失真在很低的频率范围,“经典”差分输入提供了所有熟悉的精度好处,偏置电流的消除和非常低的运算amps,反向电流噪声与宽带电流差分增益/相位性能,低电压噪声,高输出电流驱动是OPA842理想的最高动态范围的应用。

1.2整形电路

集成电压比较器比集成运放的开环增益低,失调电压大,共模抑制比小;但其响应速度快,传输延迟时间短,而且可将模拟信号转换成二值信号,即只有高电平和低电平两种状态的离散信号,不需外加限幅电路就可直接驱动TTL、CMOS等集成数字电路。我们采用高速比较器TLV3501。

1.3 FPGA和液晶显示模块

本设计采用台湾友晶Altera DE0-Nano FPGA入门学习开发板,DE0-Nano展示了一个紧密型的FPGA开发平台适用于诸如自动控制装置和便携式项目的原型电路设计,该平台采用了有着22320个逻辑单元的Cyclone IV芯片实现了尽可能的简易设计。

采用现场可编程门阵列(FPGA)为控制核心采用现场可编程门阵列(FPGA)为控制核心,利用VHDL 语言编程,下载烧制实现。将所有器件集成在一块芯片上,体积大大减小的同时还提高了稳定性,可实现大规模和超大规模的集成电路,测频测量精度高,测量频率范围大,而且编程灵活、调试方便。

利用FPGA高速的信号采集处理能力,采用等精度测量频率,在整个频率范围内测量都能达到相同的精度,不随频率的变化而变化。

JLX12864G-332 图像型点阵液晶模块使用方便、显示清晰,广泛应用于各种人机交流面板。JLX12864G-332 可以显示 128 列*64 行点阵单色图片。

2、提高抗干扰的措施

采取抗干扰措施以提高仪器灵敏度。具体措施:①数字地与模拟地严格划分,并于电源模块滤波前一点落地;②各单元供电在线路板上多加装去耦滤波电容以旁路电网干扰,对高低频信号干扰信号具有很强的抑制能力;③由于输入信号的变化可能很大,在大信号时能满足要求,而在小信号时则很容易受到干扰,所以电路设计时采用大面积接地,输入引线采用高频监控电缆以消除外界的电磁场干扰。

测试结果及分析

1、测试条件与仪器

测试条件:实验室环境,硬件电路与系统原理图完全相同,硬件电路保证无虚焊。检查多次。

测试仪器:数字示波器、数字万用表、低频信号发生器、高频信号发生器。

2、测试方法

使用信号发生器产生1hz到10Mhz的频率,用标准频率计测得标准频率,再用设计的频率计测得频率,最后求出误差。

3、测试分析

经过实测,表明本设计方案是科学的,合理的。具体能测出以下几个信号:

可以检测1Hz-100MHz的正弦信号,被测信号的有效值电压范围为10mV-1V,测量相对误差的绝对值小于10^-4。

可以检测1Hz-5MHz的方波信号,被测信号的有效值电压范围为50mV-1V,测量相对误差的绝对值小于10^-2,被测时间间隔范围0.1us-100ms,测出信号的占空比10%-90%,显示的分辨率为0.1%。

结论

本次设计是基于FPGA的等精度数字频率计的设计。在高速时钟随处可见的现代电子系统,有着非常广泛的研究价值,经实验验证,该频率计达到设计要求,可以改变数字频率计的测量范围,具有较高的整体性和可靠性,而且容易生产造价比较低,具有较好的市场前景。与传统的频率计相比,利用FPGA设计的频率计提高了系统设计的实用性和可靠性,而且实现数字系统的软件化是数字逻辑设计的趋势。

参考文献:

[1] 周立功等.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006.

[2] 莫琳.基于FPGA的等精度频率计的设计与实现[J].现代电子技术,2004,23 (10):81-82.

[3] 张杰,姚剑,叶林等.频率测量的新方法[J].工业仪表与自动化装置,2003,29(1):63-65.

基金项目:浙江海洋学院2015年度大学生科技创新项目。

(作者单位:浙江海洋学院)endprint