基于汉明码校验的AES数据加密记录器设计*

2015-12-07魏汉明刘文怡关咏梅张彦军张国佳

魏汉明,刘文怡,关咏梅,张彦军,张国佳

(1.中北大学 电子测试国家重点实验室,山西 太原030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原030051;3.北京宇航系统工程研究所,北京100076)

基于汉明码校验的AES数据加密记录器设计*

魏汉明1,2,刘文怡1,2,关咏梅3,张彦军1,2,张国佳1,2

(1.中北大学 电子测试国家重点实验室,山西 太原030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原030051;3.北京宇航系统工程研究所,北京100076)

以FPGA为硬件设计平台,实现AES数据加密记录器,重点讲述了AES算法的FPGA实现。利用MATLAB软件完成算法的密钥扩展及S盒设计,使其在硬件中的设计简化为查表操作;整体算法的设计采用流水线技术,提高了加密速度。同时,设计了汉明校验码解决由于NAND Flash位翻转经加密后带来的误码扩散的问题,将最后的纠错工作设计在计算机上完成,降低对硬件读数的影响,同时提高了系统的可靠性,该设计具有一定实用价值。

高级加密标准;汉明码;FPGA;Nand Flash

0 引言

数据记录器是遥测系统中重要的组成部分,可为飞行器的质量评估及飞行器的技术改进提供数据依据。近些年半导体技术高速发展,固态记录器以成为飞行记录器的发展趋势,在现有的固态存储介质中,基于 NAND技术的非挥发性存储器Flash(闪速存储器)以其体积小、功耗低、密度大、编程和擦除速度快、成本低等优点而被广泛地运用于各个领域[1]。

同时为了防止数据记录器中的信息被对手截获,需要对信息进行保密防护,常用的措施为采用加密编码[2-3]。加密编码对基于 Nand Flash芯片的数据记录器会产生一个问题。Nand Flash芯片的物理特性使其在使用中有可能出现位翻转的问题,即在一定的数据块中产生了一比特的误码,这个误码经过加密编码后会引起误码扩散。如数据在采集后以16 B分组,经加密编码后存入Flash芯片中,若在Flash芯片中出现了位翻转错误,那么该位所在的128 b加密数据在解密后一般得不到原来的明文数据,那么原来出现在1 B的误码经加密后扩散到了16 B中。由此可见,在加密存储系统中,对误码的控制设计尤为重要。汉明码的二元线性分组码中编码效率高,简单实用,在分组数据内能实现错误检测和1比特的误码纠正[4]。本文将研究数据记录器的AES加密设计及基于汉明码的误码控制设计。

1 系统方案设计

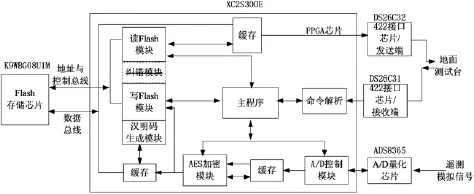

AES加密数据记录器主要完成对遥测模拟信号的采集、加密及存储,同时嵌入汉明校验码增强存储的可靠性;记录器中存储的数据最后被读取至计算机终端,完成解密与分析。记录器不能与计算机终端直接通信,配套地面测试台设备是计算机终端与数据记录器通信的桥梁。在传统方案中,误码的纠错工作在记录器中完成,数据从Flash中读出时首先要在记录器中缓存,等到误码检测与纠错工作完成后才能将纠错后的数据上传给计算机,这样会大大降低了数据传输速度。本文设计的方案中将纠错工作交由计算机完成,这样不仅能检测和纠正 NAND Flash芯片存储的位翻转错误,减轻了硬件系统的工作量,保证了数据传输的速度,而且利用计算机能够使纠错工作结果更直观[5-6]。系统的工作方案如图1所示。

图1 系统方案框图

AES加密数据记录器以 48 kHz的频率对 6路遥测模拟信号进行采样,然后将量化后的遥测数据分组加密,加密后的数据及生成的汉明校验码写入NAND Flash芯片中。采样芯片采用ADS8365芯片,单个芯片可并行实现6路差分通道的转换,有益于小尺寸系统设计;采样精度可达16 bit。存储芯片采用三星公司的4 GB容量NAND Flash芯片K9WBG08U1M。整个加密记录器的系统设计框架如图2所示。

图2 加密记录器硬件模块框图

2 关键技术实现

2.1AES加密算法的FPGA实现

本文采用的密钥长度为 128 b,状态矩阵由 4×4 B组成,则加密的迭代轮数为 10,每一轮的步骤为:(1)字节代换(s盒替换),(2)行移位,(3)列混合(最后一轮没有),(4)轮密钥加。

字节代换即通过一个非线性的函数,将原有字节替换成对应字节的过程。其实际运算操作为:首先将字节变换到GF(28)域上的乘法逆元,再对字节进行一个仿射变换。字节代换可以简化为一个简单的查表操作,AES定义了一个S盒(及逆S盒),S盒是一个由16×16 B组成矩阵,矩阵共有 256个元素(字节)。查表时,字节的高4位作为行地址x,低4位作为列地址y,指向S盒的第x行第y列的字节。为了简化硬件的工作,本文将采用官方S盒,且将S盒内容初始化至FPGA的IP核ROM中。

行移位是一个简单的左循环移位操作。对4×4的状态矩阵,第1行不移位,第2行左移1个字节,第3行左移2个字节,第4行左移3个字节即可。

列混合是将状态矩阵与一固定矩阵相乘,状态矩阵每一列的更新方式如下式所示:

式中涉及的操作有加法(异或)和乘法,由于乘法在 FPGA中直接实现较为复杂,需要将乘法运算转换为移位和加法运算。在有限域GF(28)上,{02}乘以一字节b(x)= b7×7+b6×6+b5×5+b4×4+b3×3+b2×2+b1×1+b0×0,若该字节的最高位 b7为0,则可直接对b(x)在字节内左移 1位,最低位补0即可;若最高位b7为1则需在移位后再与{1B}异或。{03}乘以一字节时则将{03}分解为{02}+ {01}再进行运算即可。

轮密钥加即将状态矩阵与轮密钥矩阵逐位异或即可。

轮密钥由初始密钥经过密钥扩展操作得来。初始密钥由用户制定,长度为128 b,将其输入到一个4×4的矩阵中,用数组W[i]表示密钥中的某一列,则初始密钥可用W[0]、W[1]、W[2]、W[3]4个数据表示;下一轮的扩展密钥可用 W[4]、W[5]、W[6]、W[7]表示……依次,最后一轮的扩展密钥数据为 W[40]、W[41]、W[42]、W[43]。各数组之间的关系为:

(1)若i非4的倍数,则有:

(2)若i为4的倍数,则有:

式中T相当与一个复杂的函数,其具体的操作为:

①字循环:将自变量循环左移1个字节。如数组[w0,w1,w2,w3]经过字循环变换为[w3,w0,w1,w2]。

②字节代换:使用S盒对每个字节进行代换。

③轮常量异或:将前两步的结果与轮常量Rcon[j]进行异或,j表示轮数。轮常数的内容(4个字节)如表1所示,密钥扩展过程如图3所示。

用户定义了初始密钥后,由密钥扩展运算就可以得到后续的10轮密钥。为了简化硬件工作,密钥扩展工作可由计算机完成,然后将所有密钥(共 11×16=176 B)作为初始化文件载入FPGA ROM核中。这样,FPGA对于密钥的相对操作可简化为简单的查表运算。

表1 10个轮常数

图3 密钥扩展

为了加快执行速度,FPGA程序中采用流水线设计。根据AES加密算法的原理,把程序主要划分为轮密钥加、S盒替换、行变换、列混合、加密输出等5个模块。各模块之间设由握手信号进行通信,每个模块只需完成自己的任务((1)AES加密步骤;(2)输出指示信号和加密状态(数据))即可。

2.2汉明码校验设计

汉明码的FPGA实现较为简单,首先需要对数据进行分组设计。由于使用的NAND Flash是4 KB每页的结构,因此将一页的4 KB数据分为一组。将4 KB数据看成是 4 096(行)×8(列)的矩阵,数据在边写入 Flash时可边产生汉明校验码,完全不影响存数的速度,最终生成12 bit的行奇校验码、12 bit的行偶校验码、3 bit的列奇校验码、3 bit的列偶校验码,只需将这总共30 bit的校验码写入Flash当前页的备用区即可。

行校验码与列校验码可以看成是独立的,而奇校验码与偶校验码是互补的,行校验码最终指示出错的“行”(字节),列校验码最终指示出错的“列”(位),二者相结合最终能定位到整个分组数据中的某一出错位且纠错。

为了方便,以列校验码的生成做示例。设列奇校验码为L_ECCo,列偶校验码为L_ECCe,则有:

计算机软件读取Flash中的数据时也会按照同样的方式生成汉明校验码,此时设列奇校验码为L_ECCo′,列偶校验码为L_ECCe′。计算机在数据分析前对数据进行校验,那么当L_ECCo与L_ECCo′、L_ECCe与L_ECCe′分别完全相等时才认定数据存储及传输正常(这里只以列校验作说明);若L_ECCo、L_ECCo′、L_ECCe、L_ECCe′4个参数的异或结果所有位都为1,那么数据出现了可纠正的错误,出错的位地址由L_ECCo′与 L_ECCo的异或结果表示。

3 实验结果

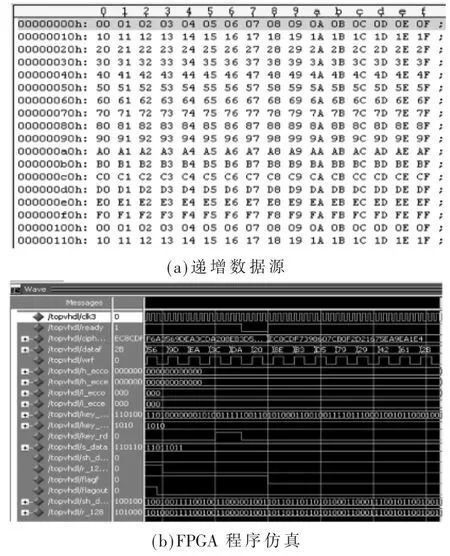

为了验证设计的正确性,对00~FF的循环递增数据进行加密存储,数据源如图4(a)所示。数据加密过程及汉明校验码生成程序仿真如图4(b)所示。加密数据最后以4 KB为单位打包上传给计算机。

图4 加密数据源及加密仿真

同时,在加密数据上传到计算机时,故意将数据中的某一位翻转,如第17 B(Byte16)的第4位(bit3),那么计算机收到的未校验的加密数据如图5(a)所示,其中字节“C0”为误码字节,直接对图5(a)数据进出解密,得到数据如图5(b)所示。数据分析报告称出现16 B的错误。由此可知,由于一个加密字节的位翻转错误,经过解密后扩散到了原16 B的分组数据中。

查看数据的汉明校验码,如图6所示,根据校验信息对数据进行纠错,再解密,数据还原正确,如图7所示,加密数据中第17 B已经由“C0”纠正为“C8”。

图5 加密数据的误码扩散

图6 校验信息

图7 数据纠错及解密还原

4 结论

本文设计并实现了基于FPGA的AES加密存储器,利用计算机软件完成部分设计(如密钥的扩展和S盒的设计)后直接例化到FPGA ROM核中,简化了硬件设计;同时采用流水线技术,加快硬件加密速度。另外,为了避免由于存储芯片NAND Flash出现的位翻转而造成加密系统的误码扩散问题,在加密数据写入存储器前设计生成了汉明校验码,而数据校验则在计算机中完成,这样能几乎不改变硬件数据读写速度,同时有效地提高了系统的可靠性。

[1]王建勋.基于NAND闪存的固态存储技术研究与实现[D].长沙:国防科学技术大学,2010.

[2]龚进.AES加密算法在电子系统中的优化及应用研究[D].太原:中北大学,2012.

[3]陈铁明,葛亮,蔡家楣,等.TinyTCSec:一种新的轻量级无线传感器网络链路加密协议[J].传感技术学报,2011,24 (2):275-282.

[4]陈铁明,白素刚,蔡家楣.TinyIBE:面向无线传感器网络的身份公钥加密系统[J].传感技术学报,2009,22(8):1193-1197.

[5]陈武.NandFlash纠错码的设计研[D].杭州:浙江大学,2011.

[6]辛英.汉明码纠错检错能力分析与应用[J].盐城工学院学报:自然科学版,2008,21(1):34.

Design of AES encryption of data recorder with Hamming code for error-check-correct

Wei Hanming1,2,Liu Wenyi1,2,Guan Yongmei3,Zhang Yanjun1,2,Zhang Guojia1,2

(1.National Key laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science&Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China;3.Beijing Insitute of Astronautical Systems Engineering,Beijing 100076,China)

Implemented with FPGA,the paper proposes a method to design data recorder with AES encryption,which is simplified with the encryption work partly done by MATLAB that is the key expansion and Subbyte box,and which is accelerated with Pipelining design.Also,Error-Check-Correct scheme is implemented in the system to resistance the error propagation problem and strengthen reliability.The final data correct work is finished on the PC to reduce its influence on the hardware reading speed.

AES;Hamming code;FPGA;Nand Flash

TH99

A

0258-7998(2015)01-0118-04

10.16157/j.cnki.0258-7998.2014060402031

国家自然科学基金项目(51275491)

2014-11-19)

魏汉明(1988-),男,在读研究生,主要研究方向:测试计量技术及仪器。