具有单层浮空场板的高压LDMOS器件研究

2015-05-31文帅,乔明

文 帅,乔 明

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

1 前言

横向双扩散效应晶体管(LDMOS,Lateral Double Diffused Metal Oxide Semiconductor Field Effect Transistor)最早是由Y. Tarui等人于1969年提出[1]。相对于标准的MOS器件,LDMOS在结构上具有以下特点:LDMOS采用的是双扩散技术,沟道长度是由两次扩散的结深之差来确定的,这就使得沟道长度可以做得很精确而不用受到光刻精度的影响,且工艺实现上简单。此外LDMOS在漏区域与沟道区之间增加了较长的低掺杂漂移区,漂移区在一定程度上缓解了MOS器件的短沟道效应。低掺杂漂移区的存在使得沟道的电阻远远小于漂移区的电阻,高阻的漂移区能够承受较大的源漏电压以及功耗,使得器件可以承受较高的耐压,因此提高了器件的耐压。并且漂移区使得栅极与漏极相隔更远,降低了栅漏寄生电容对器件频率特性的影响,提高了器件的频率特性。场板技术目前被广泛应用于高压功率器件的终端技术中。场板技术可以通过优化器件的电势分布、降低器件的表面电场峰值来提高器件的击穿电压。目前场板大致有以下几种类型:卷形阻性场板(scroll shaped resistive field plate,SRFP)[4],双层浮空场板[5~6],偏置场板[7],改进的多浮空场板modified-MFFP(multiple floating field plate)[8]等。文献[4]采用SRFP技术屏蔽HVI对横向IGBT(insulatedgate bipolar transistor)的影响,然而由于阻性场板的存在,会在其源漏电极间产生较小的漏电流,从而增加了电路的静态电流和功耗,文献[8]通过多浮空场板的应用,避免了漏电流的产生,降低了静态电流和功耗。文献[5]、[6]在横向高压器件结构中增加了第二层多晶硅场板,以产生电容耦合结构,能够更有效地优化器件表面场分布。

文章首先通过仿真软件对Double RESURFLDMOS进行了设计与优化,得到了最优设计参数,然后添加了多浮空场板结构,并对场板的数量、长度对器件耐压的影响进行了分析与研究,最后分析了场板对P-top剂量的影响,并通过仿真得到了不同场板的数量,不同P-top剂量所对应的器件耐压值。

2 高压LDMOS器件结构

具有单层多浮空场板结构的高压LDMOS器件结构如图1所示,N-epi表示n型外延层,Nepi表示其浓度;P-sub表示器件采用的是P型衬底材料,其电阻率为100 Ω·cm; P-well表示用来形成LDMOS器件沟道区的P型阱区; NP-top表示P-top的浓度;nFP表示场板的数量;dFP表示场板的长度。x方向表示沿着器件表面的方向,y方向表示垂直于器件表面的方向。

图1 具有单层多浮空场板的LDMOS器件

器件制作在n型外延(N-epi)上,外延层厚度depi为4 µm,漂移区长度为85 µm,沟道长度为1 µm,由双扩散工艺和自对准技术形成。器件采用双RESURF技术,在外延层引入一层导电类型相反的P-top掺杂区,形成结终端扩展,有效降低了器件源端和漏端的表面电场,同时p型杂质的引入使得外延层的掺杂浓度得以提高,有效降低了器件的导通电阻。器件在场氧上方有一层多晶硅多浮空场板,通过对器件表面电场的优化,能够有效提高器件的耐压。

3 结果分析与讨论

使用二维器件仿真软件Silvaco对图1中所设计的double RESURF-LDMOS器件进行了研究与仿真。

图2 外延层掺杂浓度以及P-top浓度与器件击穿电压之间的关系

图2给出了在没有场板的情况下,double RESURF-LDMOS器件在不同外延掺杂浓度和P-top浓度下所对应的耐压。当外延浓度为4.2×1015cm-3、P-top浓度为9.6×1015cm-3时,器件的击穿压值比较稳定,在760 V左右;当外延层掺杂浓度为4.0×1015cm-3、P-top浓度为9.2×1015cm-3时,器件的击穿电压值最高,为785 V左右。但是随着P-top浓度的变化,器件的击穿电压变化很大。在实际的工艺掺杂过程中,由于工艺存在一定的偏差可能会导致器件掺杂不精确,因而出现较大的耐压偏差。当外延层掺杂浓度为4.4×1015cm-3、P-top浓度为9.6×1015cm-3时,器件的击穿电压值最高,为750 V左右,此时的情况也是器件的耐压值随着P-top浓度的变化而有很大的改变。因此在实际的工艺生产中,外延层浓度最好选择4.2×1015cm-3,P-top的掺杂浓度为9.6×1015cm-3,此时器件的耐压值较平缓,也可以使得P-top的掺杂浓度有较大的误差设计范围。

图3、图4给出了器件在外延层浓度为4.2×1015cm-3、P-top的浓度为9.6×1015cm-3时,场板对器件表面电场分布的影响以及电势分布。从图3中可以看出相对于没有场板的器件结构,器件在添加场板结构后其栅场板末端的电场峰值明显降低,虽然漏端出现了较高的电场峰值,但是器件表面电场的分布总体上更加均匀,最大峰值降低,使得击穿电压由不带场板结构的755 V提高到767 V,并且可以使得带场板结构的器件能够较好地屏蔽其他因素对器件的影响。图4给出了具有场板结构器件的电势分布图,其中浮空场板是等势体,其电势由漏端到源端依次递减,形成了一个电势线性降低的趋势。

图3 有无场板对器件表面电场分布的影响

图4 带场板结构器件的电势分布

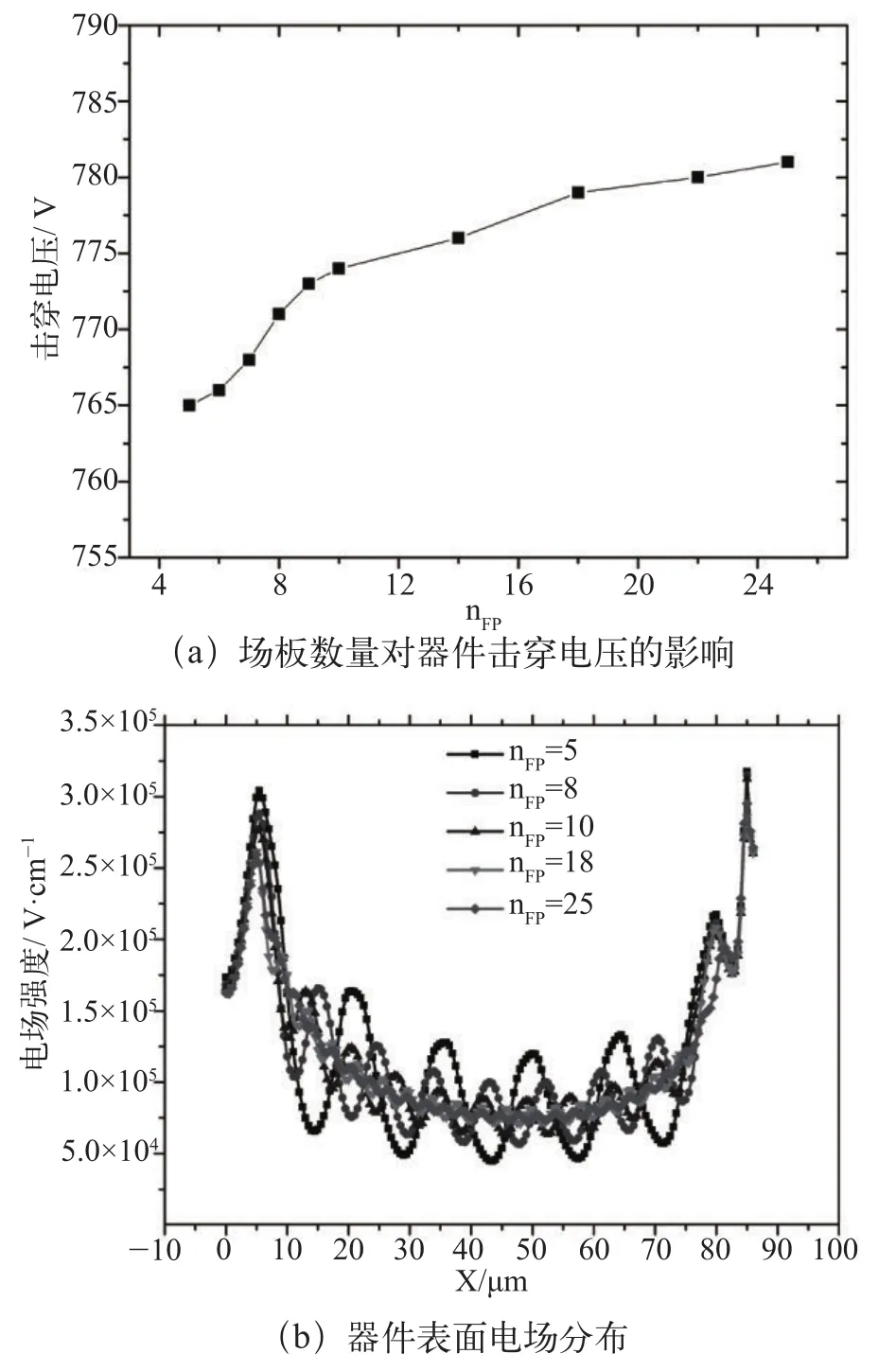

图5给出了器件在外延层浓度为4.2×1015cm-3、P-top的浓度为9.6×1015cm-3时,不同场板数量对器件击穿电压和表面电场分布的影响。当nFP=5时,场板长度为10 µm,间距为4 µm;nFP=8时,场板长度为6 µm,间距为3 µm;nFP=10时,场板长度为4 µm,间距为3 µm;nFP=18时,场板长度为3 µm,间距为1 µm;nFP=25时,场板长度为2 µm,间距为1 µm。图5(a)中所示为不同场板数量所对应的器件耐压值。根据仿真结果可以得出结论,器件的耐压值与场板数量成正比。当nFP=25时,器件的耐压可以达到781 V。但当场板的数量增大到一定数量时,耐压的增加幅度并不大,而且过多的场板会受到工艺条件的限制,因此选择合适的场板数量是很有必要的。图5(b)所示为不同场板数量对应的器件表面电场分布。场板数量越多,其表面电场越均匀,左侧栅场板末端电场峰值也随着场板数量的增加而减小,并且漂移区的电场分布更为均匀。因此,场板对于器件表面电场的优化效果比较明显,对器件的耐压也有一定的提升。

图5 场板数量对器件击穿电压的影响以及器件表面电场分布

图6 场板长度对器件击穿电压的影响

图6给出了器件在外延层浓度为4.2×1015cm-3、P-top的浓度为9.6×1015cm-3时击穿电压与场板长度之间的关系。可以明显看出随着场板长度的增加,器件的耐压值随之降低。由于每个浮空场板相当于一个等势体,与邻近的场板形成电容结构,场板上的电势由漏端到源端依次降低,并且趋于线性降低,使得电场的分布较为均匀。根据不同场板长度下器件表面电场的分布可以看出,场板长度越短,器件的表面电场分布就更为均匀,峰值就越低,尤其是栅场板末端处的电场峰值。因此,在实际设计中,可以适当降低场板长度,使得器件的表面电场得到更好的优化。

图7给出了通过工艺仿真得到的器件在外延层掺杂为4.2×1015cm-3时场板数量对double RESURF器件P-top剂量的影响。从图中可以看出,器件在没有场板的情况下,P-top剂量为1.0×1012cm-2时其击穿电压值最大,但是邻近的P-top剂量值使得器件的耐压大幅降低,在实际工艺中,可能由于工艺原因,会使得P-top的剂量与浓度出现偏差,实际的击穿电压值可能会很低。当器件添加场板结构后,对于不同剂量的P-top,器件的耐压能够较为稳定,并且随着场板数量的增加,一定范围内变化的P-top剂量对器件的耐压影响不大。由于场板数量较多时对器件表面的电场优化效果更好,降低了器件表面电场的峰值,限制了P-top的剂量对器件耐压的影响。此外,由于场板的存在,使得任意剂量的P-top可以应用于高压功率器件而不会使击穿电压降低,因此可以在一定程度上改变P-top剂量,从而在保持器件耐压的同时也可以有效降低器件的导通电阻,实现高耐压低导通电阻的器件。

图7 场板数量对double RESURF器件P-top剂量的影响

4 结论

场板技术可以通过优化器件的电势与电场分布来改善优化器件的表面电场。对于单层浮空场板结构,增加场板数量、降低场板长度能够有效优化器件表面电场的分布,增加器件的耐压,但是受到工艺和特征尺寸的限制,需要对单层多浮空场板进行数量上的优化。单层多浮空场板对double RESURFLDMOS器件的P-top剂量也具有一定的影响,在没有场板的情况下,P-top剂量的变化会使得器件的耐压出现较大的变化,从而降低了P-top的容限度。场板结构能够改善这种问题,使得器件的击穿电压随着P-top剂量的改变而不会发生太大的变化,这就使得器件的P-top层剂量可以在较大范围内选择,从而优化漂移区的掺杂总量,改变器件的导通电阻。

[1] 云振新,戴洪波. RFLDMOS功率晶体管及其应用[J]. 半导体情报,2001,38(3):16-20.

[2] Falck E, Gerlach W, Korec J. Influence of interconnections ontothebreakdown voltageof planar high-voltage pn junctions[J]. IEEE Trans Electron Devices, 1993, 40: 439.

[3] Qiao Ming, Fang Jian, Li Zhaoji, et al. HVIC with coupled level shift structure[J]. Chinese Journal of Semiconductors,2006, 27(11): 2040.

[4] Endo K, BabaY, Udo Y, et al. A 500 V 1 A 1-chip inverter IC with a new electric field reduction structure[J]. Proc ISPSD, 1994: 379.

[5] Terahima T, Yamashita J, Yamada T. Over 1000 V n-ch LDMOSFET and p-chLIGBT with JI RESURF structure and multiplefloating field plate[J]. Proc ISPSD, 1995: 455.

[6] Zhang Min, Li Zhaoji. Design of floating field plate using automatic layout generator[J]. Chinese Journal of Semiconductors, 1999, 20(8): 694.

[7] Murray AFJ, LaneWA. Optimization of interconnectioninduced breakdown voltagein junction isolated IC’s using biased polysilicon field plates[J]. IEEE Trans Electron Devices,1997, 44: 185.

[8] Shimizu K, RittakuS, Moritani J. A 600 V HVIC process with a built-in EPROM which enables new concept gate driving[Z]. ProcISPSD, 2004: 379.