基于低阈值单元的高性能低功耗设计方法*

2015-03-19倪灿灿赵振宇唐皓月曲连华

倪灿灿,赵振宇,唐皓月,曲连华,李 欢,李 鹏,邓 全

(国防科学技术大学计算机学院,湖南 长沙410073)

1 引言

速度、功耗与面积是高性能微处理器芯片设计的主要性能指标,它们互相制约,难以兼得,因此在设计初始阶段需要根据设计目标确定设计指标。以高速度为目标的设计,则难以避免功耗的增加;以低功耗为目标的设计,则必将引起性能下降。

过去数十年中已经出现很多高性能与低功耗的均衡设计,突出的有多阈值电压技术[1]、多电源电压技术以及单元尺寸优化技术。文献[2]提出在关键路径上使用低阈值电压单元来满足电路的时序要求,在非关键路径上使用高阈值电压单元来降低电路的静态功耗。文献[3]指出器件尺寸调整与双阈值电压方法结合,可获得更高的性能。文献[4]指出阈值电压技术与时钟门控相结合是高性能低功耗设计的最优组合方式。然而,对于低功耗设计中的多阈值电压技术,目前低阈值电压除了用于时序优化之外,都是单一的使用高阈值单元来降低功耗,而忽略了低阈值单元在低功耗设计中的价值。

基于低阈值单元的优势,本文重点研究高速情况下,如何用低阈值单元做低功耗设计。研究先从标准单元库展开,介绍常用设计选择单元库和单元的方式;然后在相同延时下对组合逻辑单元和时序逻辑单元进行内部功耗分析;接着用反相器链时序电路来验证低阈值电压在相同周期下做低功耗设计;最后用Benchmark和AES电路在两种阈值下相同时钟周期的情况分别综合,分析各个相同时钟周期下的最佳低功耗设计的阈值电压。

2 标准单元功耗分析与选择

40nm 标准单元库包含有几百种标准单元,根据电路设计具体需求可做不同选择。工艺厂商按照标准单元的特征将它们分门别类。阈值电压有HVT(High Voltage Threshold)、RVT(Regular Voltage Threshold)和 LVT (Low Voltage Threshold)三种。其中,HVT 静态功耗最低,用于降低静态功耗的设计中;LVT 速度最快,用于高速度设计;RVT 则应用于大多数的设计。标准单元库中的每种类型的标准单元尺寸都有多种,其性能、功耗、面积也不同。

接下来就40nm 标准单元库中典型的标准单元:缓冲器、反相器、与门、或门、D 触发器,对它们的高低阈值两种标准单元在相同延时下做内部功耗研究,注意内部功耗的衡量单位是pJ[5]。

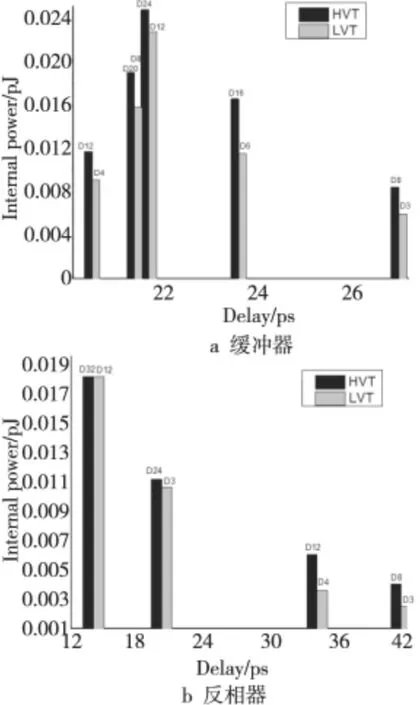

图1a,横轴为延时,纵轴为缓冲器在相同延时下的高低阈值单元对应的内部功耗。可以看出,在相同的延时下,低阈值单元产生的内部功耗要小于高阈值单元产生的内部功耗,原因是在相同的延时下,低阈值单元用的尺寸较小(D3、D4、D6、D8),与之对应高阈值单元用的尺寸则较大(D8、D12、D16、D20、D24);这些高阈值单元尺寸较大,因此会产生比低阈值小尺寸单元更大的内部功耗。同理,反相器也是如此。

Figure 1 Internal power consumption of buffers and inverters during the same delay图1 缓冲器和反相器在相同延时下的对应的内部功耗

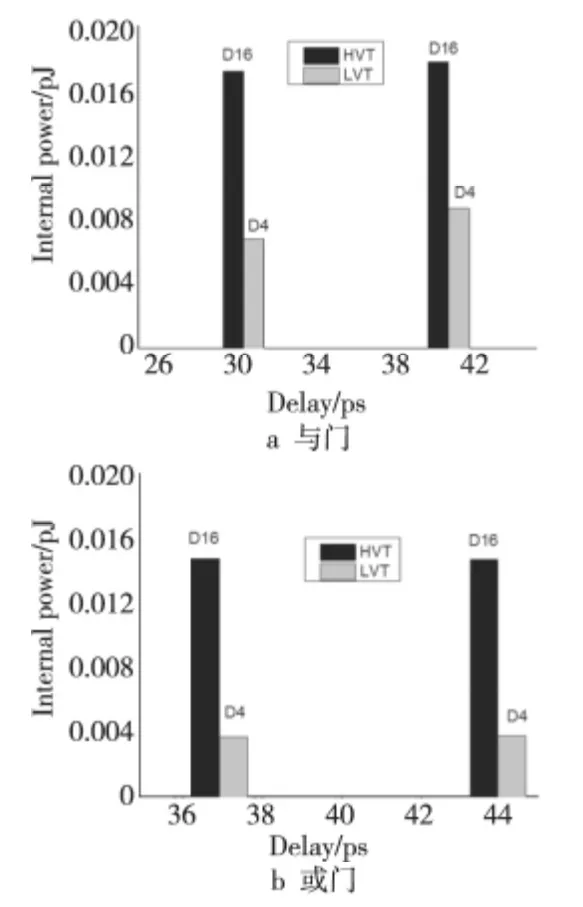

图2描述的是与门和或门的内部功耗,同理可以看出,与门和或门在相同延时下的小尺寸,低阈值单元对应的内部功耗要小于较大尺寸的高阈值单元引起的内部功耗。

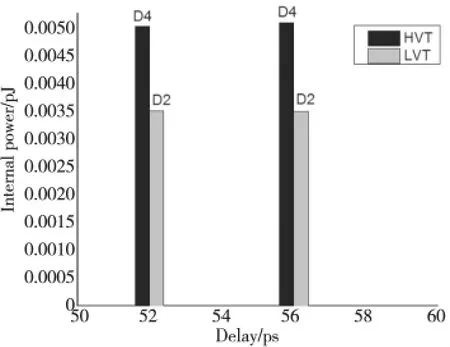

前面已经分析组合逻辑单元的情况,接下来对时序逻辑单元进行分析。图3是D 触发器的内部功耗,可以看到,在相同延时下的小尺寸低阈值D触发器对应的内部功耗要小于较大尺寸的高阈值D 触发器引起的内部功耗。

综上分析,相同延时下,选择合适的较小低阈值标准单元产生的内部功耗要小于较大尺寸的高阈值单元产生的内部功耗。

3 时序电路功耗分析与验证

Figure 2 Internal power consumption of and gate and or gate during the same delay图2 与门和或门在相同延时下对应的内部功耗

Figure 3 Internal power consumption of flip-flop during the same delay图3 D 触发器在相同延时下的对应的内部功耗

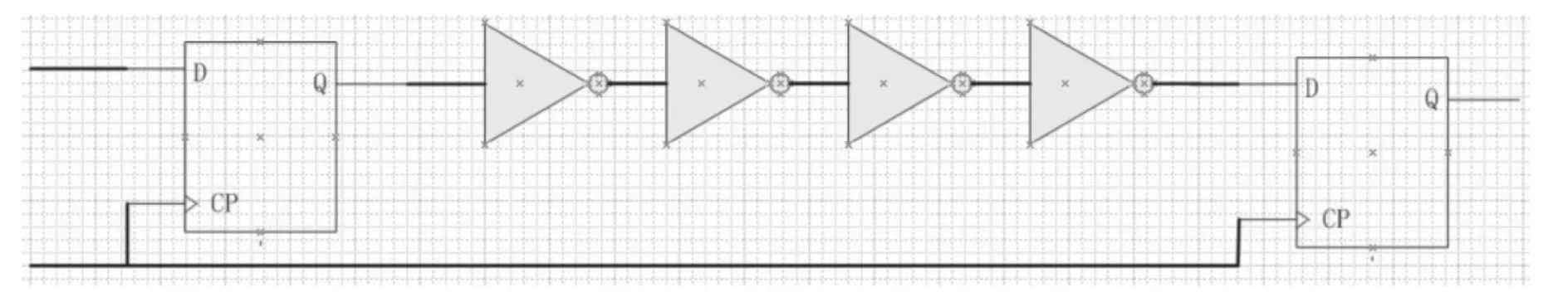

分析完单个的标准单元后,再分析一条链路上HVT 与LVT 的动态功耗关系。由第2节的结论知道,在相同的速度下(延时),LVT 用比HVT 很小的尺寸就可以达到,同时得到的动态功耗值要比HVT 的值小很多。接下来,对三级、四级、五级反相器链进行实验;并以图4四级反相器链组成的时序电路进行详细分析。图4 中两端为D 触发器,中间为尺寸优化后的反相器链。参考文献[6]给出了使得延时最小的反相器链尺寸的确定方法,每个反相器的最优尺寸为:

其中,Cg,j为第j级的栅电容与线电容之和,Cg,j-1、Cg,j+1为Cg,j的上一级和下一级的电容。40nm 工艺的线电容为0.2~0.3fF/μm,预估本电路反相器链的线电容为10fF。经过计算,HVT标准单元四级反相器链的尺寸分别为INVD3、INVD8、INVD16、INVD24;此尺寸下的延时最小,速度最快。

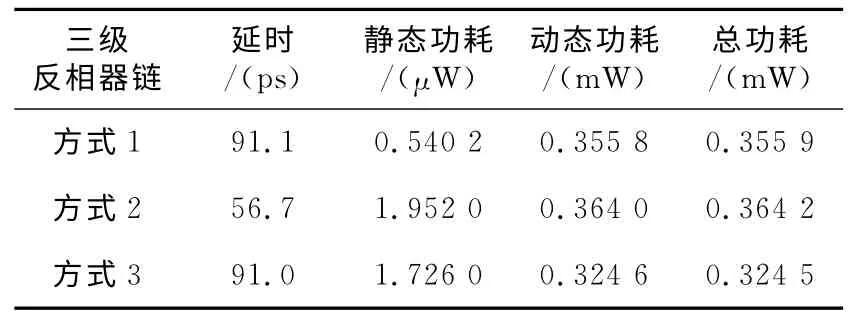

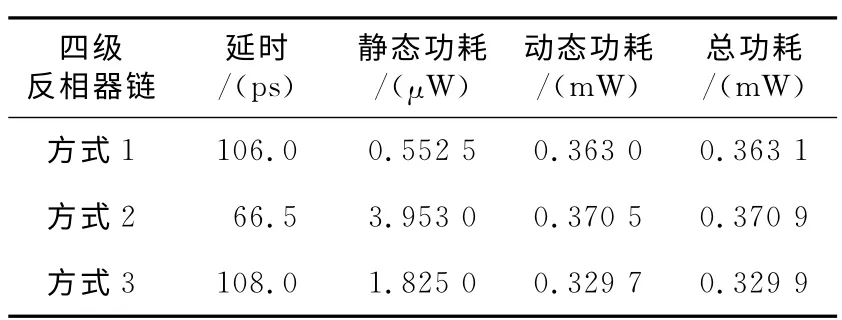

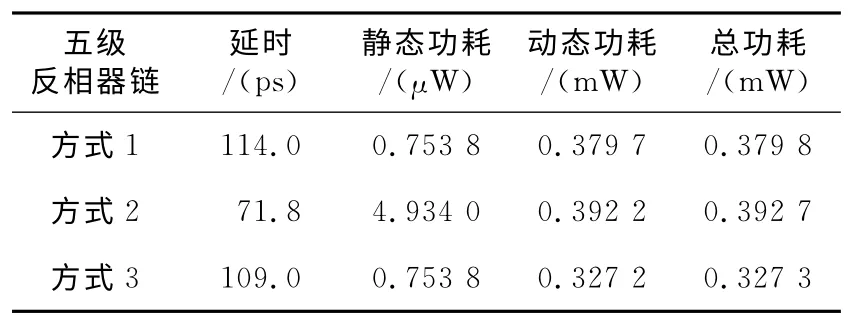

表1~表3 为三级、四级、五级反相器链的时序与功能。表2方式1从时钟输入到第二级触发器的D 数据输入端所耗的延时为106ns,几乎达到了最大的时钟周期,动态功耗为0.363mW。第2种实现方式为替换标准单元阈值为LVT,达到的延时大大减小,而动态功耗增加了2.89%。方式3 在满足高速的情况下,延时为108ns,缩小LVT 的尺寸为D1、D1、D2、D2 来降低动态功耗,其值为0.329 7mW,下降了9.17%,虽然LVT 静态功耗相对HVT 增加了3倍,但是带来动态功耗显著降低,从而得到最终的总功耗的降低,下降9.4%。同理表1 三级反相器链的方式3 下降了8.8%,表3 五 级 反 相 器 链 的 方 式3 下 降 了13.8%。换句话说,在相同时钟周期下,LVT 可以通过尺寸的缩放带来动态功耗的降低,进而带来总功耗的降低。

Table 1 Timing and power consumption information of three-level inverter chain表1 三级反相器链的时序与功耗信息

Table 2 Timing and power consumption information of four-level inverter chain表2 四级反相器链的时序与功耗信息

Figure 4 Inverter chain timing circuits图4 反相器链时序电路

Table 3 Timing and power consumption information of five-level inverter chain表3 五级反相器链的时序与功耗信息

4 IC设计综合与结果分析

经过前面的单个标准单元和一条反相器链的分析后,我们发现,可以通过LVT 单元降低动态功耗来降低总功耗。对于门的类型选择,主要在综合阶段、布局布线阶段以及ECO(Engineering Change Order)阶段。本小节分别对高低阈值电压进行综合,分析动态功耗占据总功耗比例大和小的两种电路用何种阈值电压综合得到的功耗更低,以及在什么样的时钟周期下对应哪种阈值电压综合出的功耗更低。所采用的电路一种是基于Benchmark的测试电路,并选择ISCAS89 系列电路中的S1423做基准电路,它包含600个门的规模;另一种是对AES电路进行综合,其规模约为7 000个门。

4.1 综合结果分析

4.1.1 S1423总功耗结果分析

当HVT 设置的时钟周期小于1.1ns时,松驰slack出现负数,LVT 在小于1.0ns时,slack出现负数。此时在小于1.0ns这个极限时钟周期下,如果可以通过布局布线阶段修复时序,那么在1.0ns到1.1ns之间的时钟周期,即LVT 的slack为0,HVT 的slack刚好小于0,得到的LVT 功耗为0.195 4 mW,HVT 的功耗为0.207 mW,即LVT 的功耗更低。

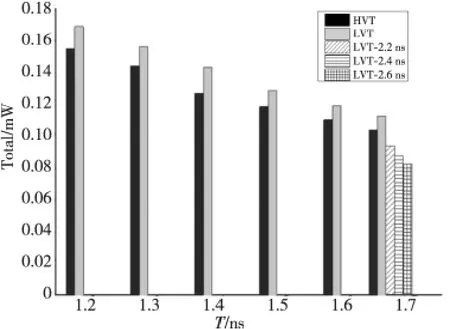

当设置的时钟周期大于1.67 ns 后,采用LVT 的slack会出现裕量,因此对于图5的1.2ns到1.67ns之间的时钟周期,可以看出HVT 的总功耗更低。

当设置的时钟周期增加到一定值后,HVT 与LVT 的时钟周期始终为2.1ns与1.67ns,不会随着周期设定值增加实际的时钟周期值也增大。图中LVT-2.2ns表示设置的时钟周期为2.2ns,但是实际的时钟周期为1.67ns。即在设定的时钟周期大于1.67ns 后,从图LVT-2.2ns、LVT-2.4ns、LVT-2.6ns可以看出,LVT 综合的功耗更小。

Figure 5 Total power of S1432in the same clock cycle图5 S1432在相同时钟周期下的总功耗

4.1.2 AES总功耗结果分析

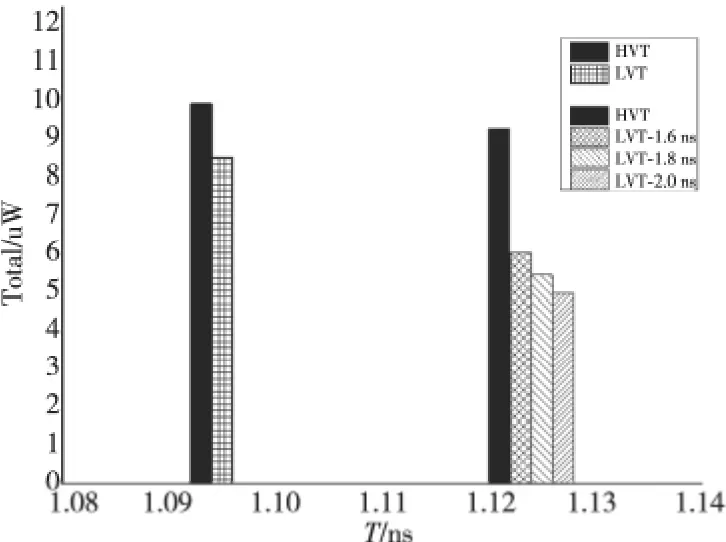

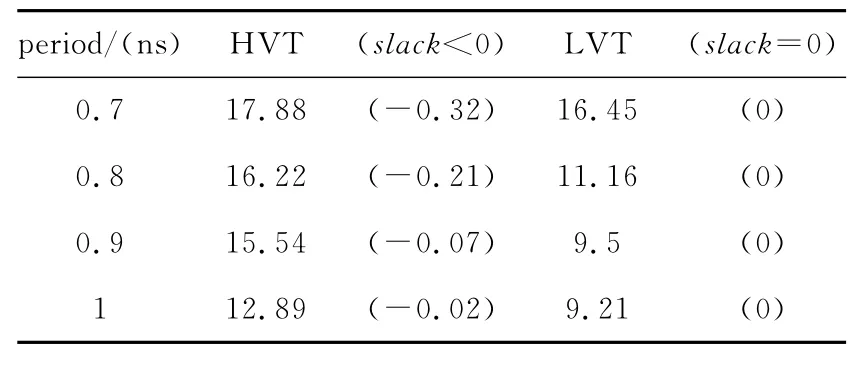

对于AES电路在HVT 条件下时钟周期小于1.1ns时slack出现负数;而LVT 则是在时钟周期小于0.6ns时slack出现负数。此时如果在0.6 ns到1.1ns之间这种极限时钟周期下通过物理设计阶段修复时序,那么在0.6ns到1.1ns之间的时钟周期测出的功耗值如表4所示。可以看出,在LVT 的slack为0、HVT 的slack刚好小于0时,LVT 综合出的功耗更低。

当设定的时钟周期大于1.1ns后,LVT 和HVT 的slack都为正。从图6 可以看出,无论有没有时序裕量,LVT 综合出的总功耗都小于HVT综合出的总功耗。因此,在相同时钟周期下,AES电路用LVT 综合出的总功耗更低。

Figure 6 Total power of AES in the same clock cycle图6 AES在相同时钟周期下的总功耗

Table 4 Power consumption across the design compiler in the same clock cycle表4 AES在相同时钟周期下综合的总功耗

4.2 观察分析

4.2.1 S1423电路分析

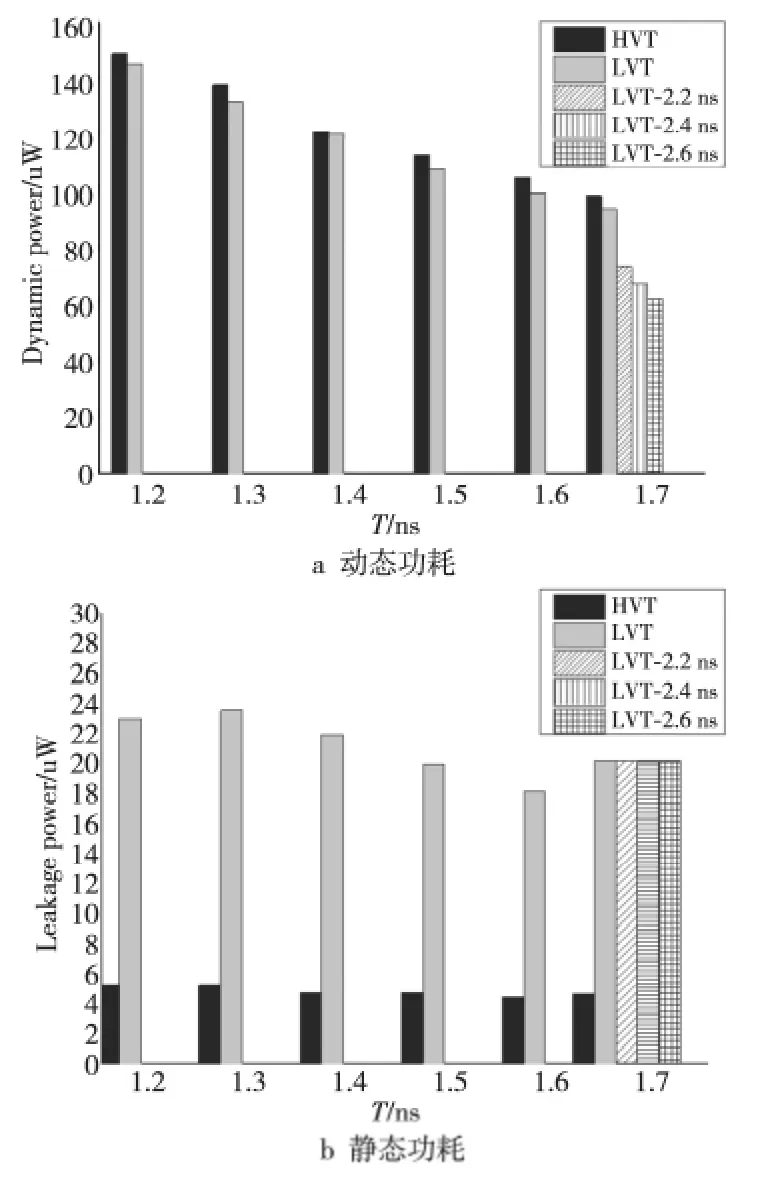

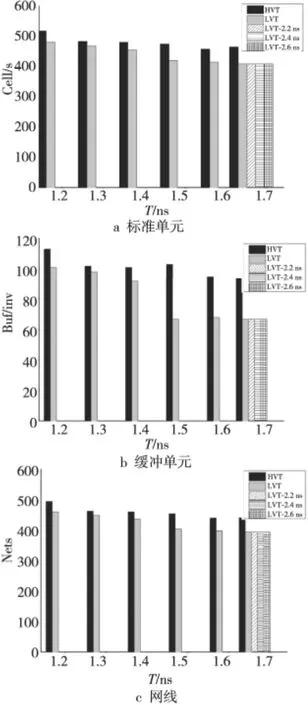

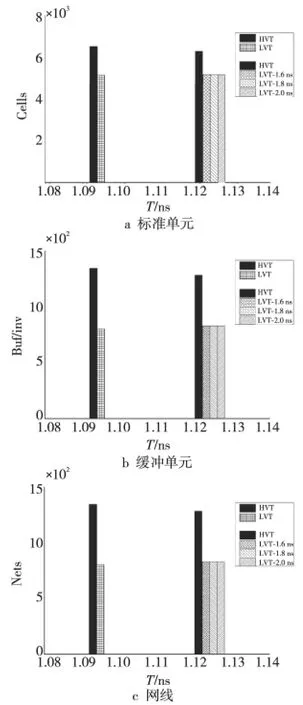

对于S1423电路的总功耗分析,本文从动态功耗和静态功耗两方面分别进行分析着手。一方面电路的动态功耗来自标准单元产生的内部功耗以及网线负载产生的动态开关功耗。如图7a所示,在1.1ns到1.67ns之间,LVT 综合出的动态功耗要小于HVT 综合出的动态功耗,原因从图8可以看出。图8中横轴为各个时钟周期,图8a纵轴为对应的两种高低阈值综合出的标准单元数目,图8b为缓冲器数目,图8c为网线负载数目。HVT综合的标准单元数目比LVT 多,多出3.2%~13.1%;缓冲单元数多出4.1%~53.7%。这些多余出来的单元会产生额外的内部功耗,而内部功耗值占动态功耗的60%左右。因此最终LVT 单元综合出来的动态功耗要小于HVT 单元综合出来的动态功耗。另一个重要的原因来自于网线负载产生的动态开关功耗。如图8b 所示,可以发现,HVT 综合出来的网线数目要比LVT 综合出来的数目高出3.2%~12.6%,这些多出的网线又产生额外的开关功耗,这部分开关功耗占总功耗的30%以上。最终LVT 动态功耗比HVT 的降低4%左右。

Figure 7 Dynamic power and static power of S1423in the same clock cycle图7 在相同时钟周期下的动态功耗和静态功耗

另一方面,从图7b可以看出,LVT 综合产生的静态功耗是HVT 的5倍以上,而该S1423电路的LVT 静态功耗部分占总功耗的17%左右,因此最终的结果是:由于静态功耗占总功耗的比例较大,使得LVT 产生的静态功耗增大的量要大于LVT 产生的动态功耗降低的量,从而总功耗未能降下来。

Figure 8 Numbers of standard cells,buffer cells and nets of the S1423across the design compiler in the same clock cycle图8 S1423 在相同时钟周期下综合出的标准单元、缓冲单元和网线数目

因此对于静态功耗占总功耗大的电路:当LVT 的slack为0、HVT 的slack为负时,用LVT综合的功耗更低;当HVT 和LVT 的slack都为0时,HVT 综合的总功耗更低;当slack为正时,从图7可以看出,静态功耗没有变化,但是动态功耗进一步下降,约降低9%左右,从而LVT 综合的总功耗要小于HVT 综合的总功耗。从图8可以看出,在slack为 正 时(LVT-2.2ns,LVT-2.4ns,LVT-2.6ns),单元数目以及网线负载数目都没有变化。原因一是综合的时钟周期达到最优后,时钟周期不会再降低,但动态功耗随着设定的时钟周期值增大而缓慢减小;原因二是足够的时序裕量还有更优的逻辑重组,这可以得到更低的动态功耗。因此,在设置的时钟周期LVT 有时序裕量,即slack为正的情况下,用LVT 综合产生的功耗更低。

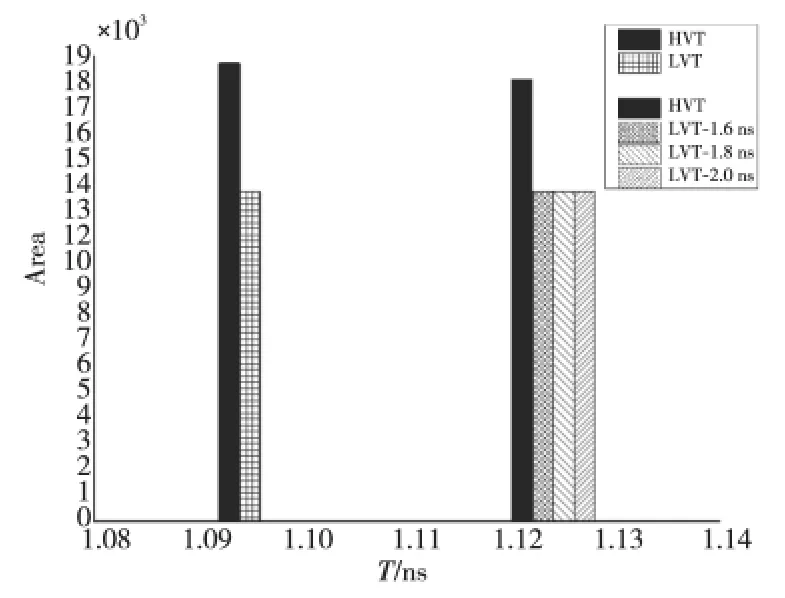

从图9可以看出LVT 单元综合出的面积比HVT 单元综合出的面积小15%左右。原因是这些面积是标准单元的总数目与相应单元面积的乘积之和,而前面已经分析,LVT 综合出的标准单元数目更少,从而具有面积优势。

4.2.2 AES电路分析

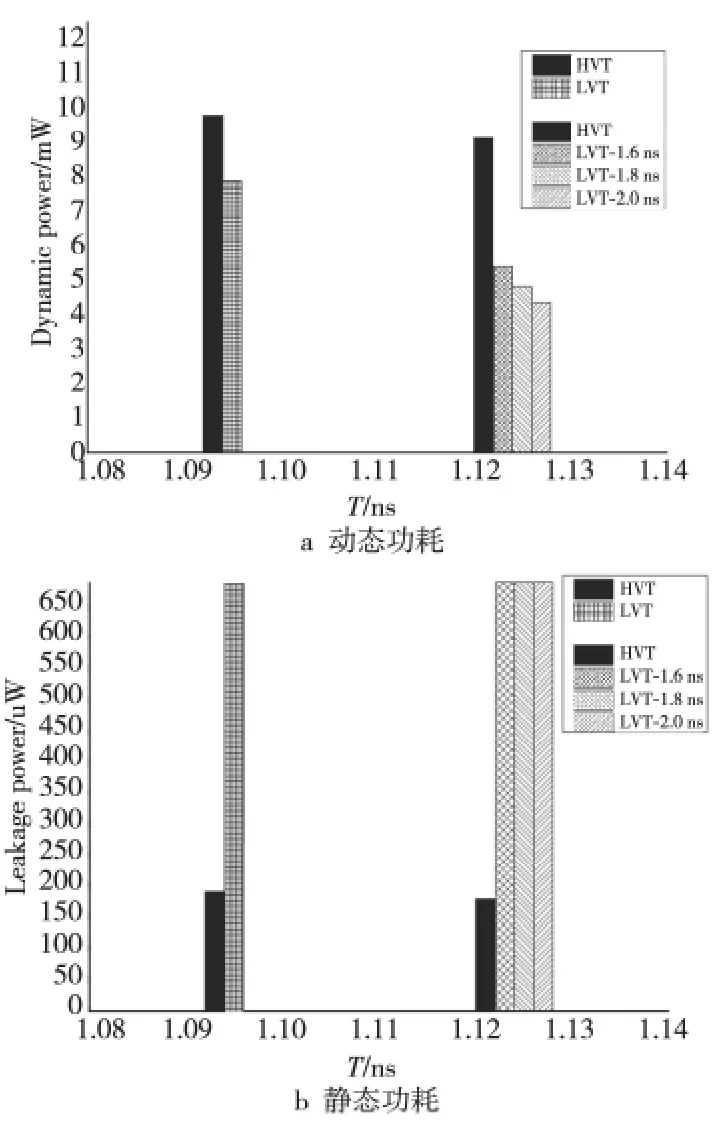

如图10a所示,在1.1ns时,slack为0。可以看出,LVT 综合出的动态功耗要小于HVT 综合出的动态功耗,原因从图11可以看出。

Figure 10 Dynamic power and static power of AES in the same clock cycle图10 AES在相同时钟周期下的动态功耗和静态功耗

Figure 11 Numbers of standard cells,buffer cells and nets of the AES across the design compiler in the same clock cycle图11 AES在相同时钟周期下综合出的标准单元、缓冲器以及网线数目

图11a中HVT 比LVT 综合的标准单元数目要多20.9%,图11b中HVT 比LVT 综合的缓冲单元数目多40.1%。这些内部功耗值占动态功耗的75%左右。从图11c可以发现,HVT 综合出来的网线数目要比LVT 综合出来的网线数目高出21%,这些多出的线产生的开关功耗,占总功耗的15%左右。最终LVT 动态功耗比HVT 的降低20.4%左右。LVT 综合出的动态功耗要小,但是从图10b可以看出,LVT 综合产生的静态功耗是HVT 的5倍以上,而该AES电路的静态功耗部分占总功耗的8.9%左右,因此由于静态功耗占总功耗的比例不大,使得LVT 产生的静态功耗增量要小于LVT 产生的动态功耗降低的量,从而总功耗降低。当出现时序裕量时,即slack为正,下图10a的LVT1.2ns,LVT1.4ns,对应的实际时钟周期依然为1.1ns;LVT1.6ns,LVT1.8ns,LVT2.0ns对应的实际时钟周期为1.12ns。从图10可以看出,静态功耗没有变化,但是动态功耗进一步下降,约降低40.8%左右,从而LVT 综合的总功耗要小于HVT 综合的总功耗。从图11 可以看出,单元数目以及网线负载数目都没有变化。原因与S1423电路一样。因此,对于动态功耗占的比例大的电路,用LVT 设计功耗比HVT 更低并且有时序余量时,相比较总功耗降低得更多。

从图12可以看出,LVT 单元综合出的面积比HVT 单元综合出的面积小28%。而前面已经分析,LVT 综合出的标准单元数目更少,从而带来更小的面积优势。

Figure 12 Total area across the design compiler in the same clock cycle图12 在相同时钟周期下综合出的面积

4.3 不同端角下功耗分析

以上实验都是基于TT(0.9V,25℃)端角下的研究;AES电路在1.1ns周期下,用HVT 单元综合用了7 860 个 门 和5 423 条 网 线,而 通 过LVT单元综合只用了5 958个门和6 849条网线,节省了24.2%的门数和20.8%的网线。因此,用LVT单元综合的门级网表对提供给后端做物理设计,它的优势体现在逻辑门数和网线的减少。在物理设计阶段由于短路径等LVT 单元还可以替换为HVT 单元降低静态功耗,最终在不同端角尤其是FF Corner下由于HVT 的一些替换而减少了“结温”引起的静态功耗问题,从而实现了用LVT 综合出门和网线数量较少的门级网表,为后端物理设计提供了一个更优的起点,这意味着更低的动态功耗,进而达到降低总功耗的目的。

5 结束语

本文在40nm 工艺下分析了低阈值单元的内部功耗和延时特性,在高速时序电路中使用小尺寸的低阈值单元降低单元数量和网线负载来达到降低动态功耗的目的,从而验证了LVT 单元设计低功耗的可行性。因此,本文为高性能低功耗设计者提供了高低两种阈值电压选择的可靠依据。

[1] Srivastav M,Rao S S S P,Bhatnagar H.Power reduction techniques using multi-Vt libraries[C]∥Proc of the 5th International Workshop on System-on-Chip for Real-Time Applications,2005:363-367.

[2] Sarvesh H K,Dennis M S,David T B.Design-time optimization of post-silicon tuned circuits using adaptive body Bias[J].Computer-Aided Design of Integrated Circuits and Systems,2008,27(3):481-494.

[3] Karnik T,Ye Y,Tschanz J,et al.Total power optimization by simultaneous dual-Vt allocation and device sizing in high performance microprocessors[C]∥Proc of the 39th Conference on Design Automation,2002:486-491.

[4] Qureshi S,Sanjeev K R.Power and performance optimization using multivoltage,multi-threshold and clock gating for low-end microprocessors[C]∥Proc of IEEE Region 10Conference,2009:1-6.

[5] Veendrick,HarryJ M.Short-circuit dissipation of static CMOS circuitry and its impact on the design of buffer circuits[J].IEEE Journal of Solid-State Circuits,1984,19(s):468-473.

[6] Chandrakasan A.Digital integrated circuits:A design perspective[M].2nd Edition.Beijing:Publishing House of Electronics Industry,2012.