高速电路设计研究

2015-03-15黄继承黄继文彭星波

黄继承,黄继文,彭星波,张 特

(1.菏泽高级技工学校,山东菏泽274000;2.武汉邮电科学研究院光纤通信技术与网络国家重点实验室,湖北 武汉430074;3.华中科技大学计算机科学与技术学院,湖北武汉430074)

0 概 述

随着半导体工艺的发展,器件的工作频率越来越高,使得高速PCB的设计成为产品设计中的一个重要环节。低频电路设计时,电源和地可以按理想情况处理,过孔自身的ESL和ESR可以忽略不计,传输线也可以不考虑阻抗匹配。而在高频电路设计时,电源完整性和信号完整性紧密相关。地反弹噪声太大、去耦电容的设计不合适、回路影响很严重、多电源/地平面的分割不好、地层设计不合理、电流不均匀、阻抗不匹配等都可能成为电路设计的严重问题。本文理论结合实际,从叠层、阻抗匹配、走线、过孔设计、电源等多方面讲述了PCB电路设计的方法。

1 叠层设计

在设计多层PCB电路板之前,设计者首先会对元器件进行预布局,结合其他EDA工具分析电路板的布线密度、有特殊布线要求的信号线的数量和种类,确定信号层的层数;然后根据电源的种类、来确定电源层的层数;根据电源的种类隔离和抗干扰的要求确定内电层的数目。这样,整个电路板的板层数目就基本确定了。多层板设计一般遵循以下几个设计规则[1]:①每个信号层都与平面相邻;②信号层与与相邻平面成对;③电源层和地层相邻并成对;④高速信号埋伏在平面层中间,减少辐射;⑤使用多个底层,减少地阻抗和共模辐射。表1给出了多层板叠层结构参考表。

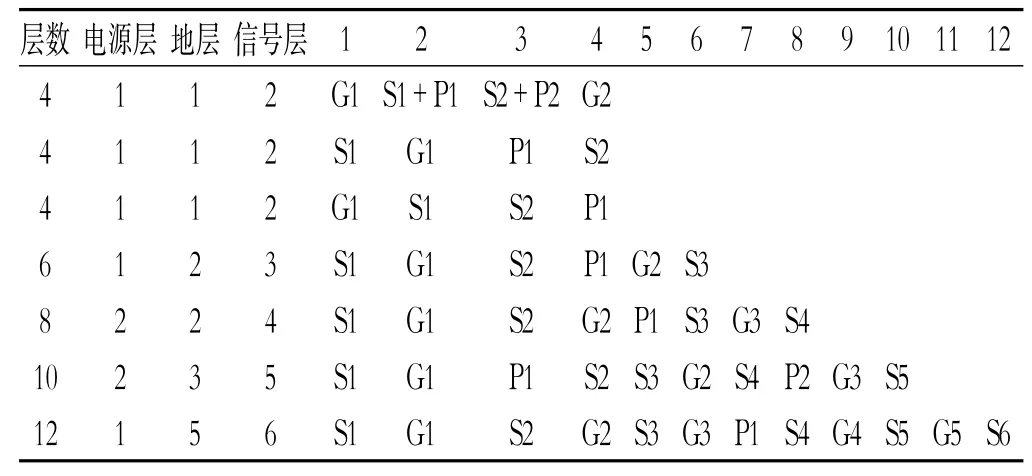

表1 多层板叠层结构参考表

二层PCB板,因其EMC效果最差,一般用于低速电路设计。本文主要以四层板为例,讲解一下PCB板层设计。

表1中的第一种结构应当是四层板中最好的。因为顶层和底层都是地层,对EMI有屏蔽作用,同时电源层和地层距离很近,电源内阻较小,取得最佳效果。当PCB板密度较大或者功耗较大时不适合采用这种叠层结构。表1中的第2种结构是最常用的。但从板的结构上看,也不适用于高速数字电路设计。因为在这种结构中,电源层与接地层的间距仍然过大,不易保持低电源阻抗。在此种结构中,由于辐射是向空间的,需加屏蔽板,才能减少EMI。表1中的第3种结构,S1层上信号线质量最好,S2次之,对EMI有屏蔽作用,但电源阻抗较大。此板能用于全板功耗大和在干扰源或者说紧临着干扰源的情况下。

除了板层设计之外,高速电路对PCB板材有更高的要求。商用无线通信要求使用低成本的板材、稳定的介电常数(εr变化误差在±1~2%间)、低的介电损耗(0.005以下)。具体到PCB板材,目前可供选用的板材很多,它们使用的场合各不相同。如FR4用于1GHz以下混合信号电路、多脂氟乙烯PTFE多用于多层高频电路板、聚四氟乙烯玻璃布纤维F4用于微波电路双面板、改性环氧树脂FR4用于家用电器高频头(500 MHz以下)。FR4板材易加工、成本低、便于层压,得到了广泛应用。为了挑战日益激烈的市场竞争,设计者必须在材料性能、成本、加工工艺难易及成品板的可靠性间采取折衷。

在使用高频板制作时,建议表面工艺优先选择镀金、沉金、喷锡、OSP工艺。因为喷锡和无铅喷锡工艺温度比较高,高频板容易有起泡等现象出现。从平整度对比:镀金、沉金、喷锡(HAL)依次递减;从可焊性上对比:镀金、沉金、喷锡(HAL)依次递增。可焊性好和平整度高的OSP工艺(涂覆有机可焊保护剂),但因自身抗氧化能力不行,一般只作样板。PCB板必须设计Mark点,否则将导致贴片效率和精度降低。PCB产品质量分为三级:一级主要用于通用电子产品;二级主要用于专业用途的电子产品;三级主要用于高可靠性电子产品。一般通信电子产品选择PCB二级。

2 阻抗匹配与端接

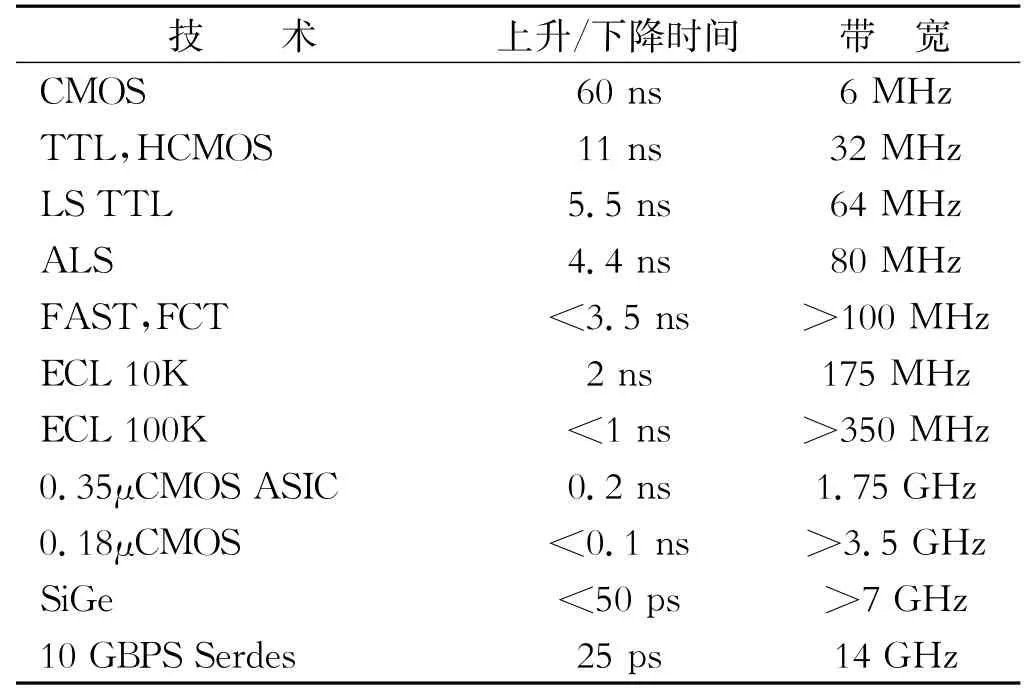

在高速PCB设计中,阻抗的匹配与否关系到信号的质量优劣。对于低频电路一般不考虑传输线的阻抗匹配,只考虑信号源跟负载之间的阻抗匹配。因为低频信号的波长很长,传输线相对于它很短,反射可以不考虑。但在高频电路中,必须考虑传输线的阻抗匹配。高频信号的波长很短,当高频信号波长可以和传输线长度相比拟时,反射信号就会叠加在原信号上改变原信号的形状。何为高速信号呢?一般认为如果信号的上升/下降时间(按10%~90%计)小于6倍导线延时,就是高速信号,必须注意阻抗匹配的问题。导线延时一般取值为150 ps/inch。表2提供了相关技术参数的上升下降时间。

表2 高速信号上升下降时间

阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,电路将获得最大的能量传输。反之则在传输中有能量损失,损失的能量反射回来,可能导致高速电路中出现振铃现象[2]。传输线的特征阻抗是指信号沿传输线传播时同一点的电压电流比。传输线特征阻抗与它所在的板层、走线宽度、覆铜厚度、PCB所用的材质(介电常数)、导线与其最近的参考平面的距离等因素有关,与传输线的长度,以及信号的幅度、频率等均无关。在PCB板上,传输线一般分为两种:微带线(microstrip)和带状线(stripline)。它们的特征阻抗可以使用软件计算,allergro计算阻抗相对于Polar Si8000这样的专业软件还是误差比较大。由于PCB的各个厂家工艺水平不一样,计算出来的阻抗值有一定误差。高速PCB布线中,把数字信号的走线阻抗设计为50Ω,10%的误差。规定同轴电缆基带50Ω,频带75Ω,对绞线(差分)为100Ω。

为了避免信号在传输线上传输时发生反射,需要把PCB传输线做成受控的传输线,并且保证特性阻抗不发生变化,把PCB板做成受控阻抗的电路板。在实际应用中,一方面尽量使PCB线各处的特性阻抗保持一致(比如:关键信号线少打过孔);另一方面PCB线的特性阻抗和输出阻抗、负载阻抗的不匹配采用终端匹配的方法来解决,也可以通过计算改变传输线的特性阻抗来解决。

实现高速信号传输的阻抗匹配可有多种方法:采用串联源端阻抗匹配消除传输线路的二次反射;采用简单并联端接、戴维南并联端接、RC终端匹配等方式实现终端的阻抗匹配。选择合适的总线终端匹配技术是保证数字系统性能最关键的要素。不合适的总线终端匹配技术可能导致信号振荡和阶梯效应,而这些效应的出现都会引起错误的触发,从而导致最终数据的错误。

3 走线设计

PCB走线的好坏将直接影响到整个系统的性能,布线在高速PCB设计中是至关重要的。布线的好坏在一定程度上影响着电路板的性能。低频电路和高频电路的特性有一些区别。在低频下,电流是沿着电阻最小的路径流回,而在高频下,电流是沿着电感最小的回路流回,也是阻抗最小的路径,表现为回路电流集中分布在信号走线的正下方[3]。因此对关键的信号线都要保证地平面的完整性以降低回流阻抗。电容的过孔要尽量靠近焊盘,连接电容和过孔的线要短而宽。电容之间不能共用过孔,每个过孔都要有自己单独的回流途径,以防止干扰。邻层最好不要有平行的走线,交叉线尽量少。重要的信号线尽可能避免不必要的过孔,尽可能在内层走高速线以降低EMI。时钟的走线越短越好,最好做包地处理。

直角走线是PCB走线中要尽量避免的情况。从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。总的来说,在1 GHz以下的应用中,直角走线产生的任何诸如电容、反射、EMI等效应在TDR测试中几乎体现不出来,而到10 GHz以上的RF设计领域,这些小小的直角都可能成为高速问题的重点对象。差分走线因抗干扰能力强,有效抑制EMI和时序定位精确等优点,而在高速电路设计中应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。在PCB电路设计中,一般差分走线之间的耦合较小,往往只占10%~20%的耦合度,更多的还是对地的耦合,所以差分走线的主要回流路径还是存在于地平面。因此对于差分信号,间距不等造成的影响是微乎其微的,相比较而言,线长不匹配对时序的影响要大得多。PCB差分走线的设计中最重要的规则就是匹配线长,其它的规则都可以根据设计要求和实际应用进行灵活处理。蛇形线也是高速PCB设计中经常使用的一类走线方式,其主要用于调节延时,以满足系统时序设计要求。但是蛇形线会破坏信号质量,所以布线时要尽量避免使用。

4 过孔设计

过孔是多层PCB设计中的一个重要因素,过孔一般又分为三类:盲孔、埋孔和通孔。在低速PCB设计中,过孔的寄生电容和寄生电感对PCB设计的影响较小[4]。但在高速PCB设计中,看似简单的过孔常常对电路性能影响很大。过孔自身对地的寄生电容主要是延长了信号的上升时间,降低了信号的速度,寄生电容值越大则影响越大。一般情况下,在高速数字电路的设计中,过孔的寄生电容带来的危害往往小于寄生电感。过孔自身存在的寄生串联电感会削弱旁路电容的作用,减弱整个电源分配系统的滤波效果。就寄生电感值而言,过孔的直径对电感的影响较小,而对电感影响最大的是过孔的长度,所以减小PCB厚度对于降低过孔寄生电感有一定效果。一般情况下,所有通孔尽量不上焊盘,以免造成焊接时反面漏锡的现象;在底层和顶层均是焊盘的情况下,可以在焊盘上打孔。为了减小过孔的寄生效应带来的不利影响,在设计中可以尽量做到:

(1)从设计需要、成本以及信号质量多方面综合考虑,选择合适大小的过孔。对于一般的PCB设计来说,可以选用10/20Mil(钻孔/焊盘)的过孔,而对于一些高密度的板子,也可以使用8/18Mil的过孔。目前技术条件下,很难使用更小尺寸的过孔了。对于电源或地线的过孔则可以考虑使用15/30Mil的过孔,以减小阻抗。

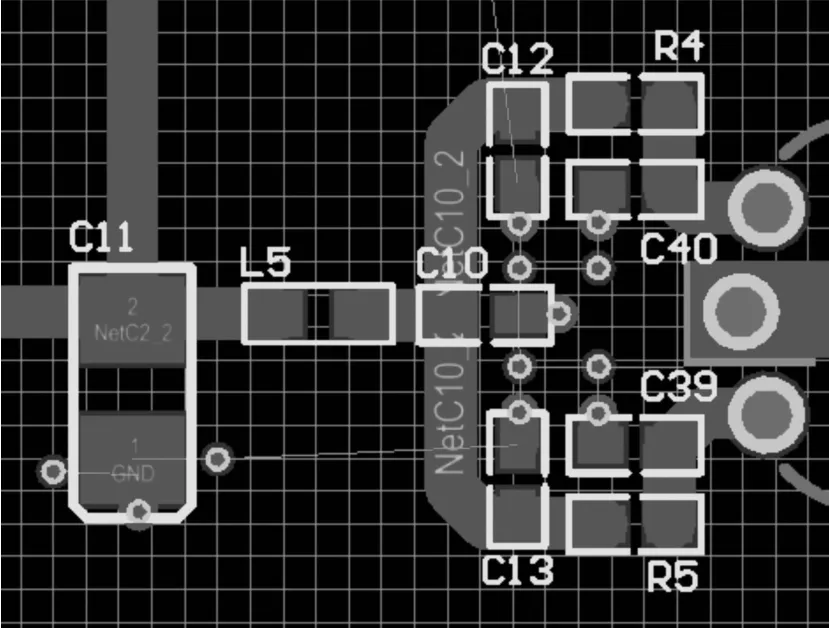

(2)PCB上的关键信号线尽可能避免非必要的过孔。在电源和地的管脚附近打过孔,过孔和管脚之间的引线要短而宽,以减小阻抗。在信号换层的过孔附近放置一些接地的过孔,以便为信号提供最近的回路。图1是一个π型滤波电路布局,电容接地附近放置多个电容,电容和过孔之间的连线短而宽。

图1 滤波电路布局

在设计过孔时应从成本,信号质量以及PCB厂家工艺等方面综合考虑。过孔越小,板上的空间就越大,同时过孔的寄生电容也越小,对高速信号的影响就越小。采用非导穿孔会增加成本,同时过孔的大小也受到PCB厂家钻孔和电镀工艺技术的制约,因此高速PCB的过孔设计应该均衡考虑。

5 电源设计

电源分配网络也是设计高速系统板时需要考虑的重要问题。理想电压源的阻抗为零,零阻抗使得电流在传输过程中无压降损失,从而负载电压使得电压源电压相等。而实际的电压源在整个电源分配系统中一定有以电阻、电感或者电容形式存在的阻抗。

电源设计的目的是尽可能减小电源分配网络中的阻抗。常用的电源分配方法有电源总线法和电源位面法两种方法。一般来说,从阻抗特征上讲,电源位面法阻抗小些;不过,从实用性上讲,总线法更好一些。电源总线系统中每种电压级别所需要的线路数目根据系统设备需要的不同而不同。电源位面系统是由多个覆铜层或者覆铜层的部分组成的。每个不同电压级别需要一个单独的整块或部分覆铜层。早期设计一般采用电源总线系统,相对而言,整个覆铜层做电源层,成本比较高。电源层和信号层在同一层,电源线相对于电源层而言,电源线比较窄,电源线宽越窄,阻抗越大。尽管电源线的阻抗很小,但是对PCB板的电源分配仍然很大。例如,一块供应总电压为5 V的PCB板,可能在总线最初给设备供电时的电压为5 V,但在最后为总线供电的电压变为4.5 V。而电源位面系统使用的是整个或部分覆铜层,相比带有同样多设备的总线系统,电源层阻抗只是总线阻抗的一个零头。因此,电源位面系统的性能更好[5]。电源总线法由于电流被限制在供电网络总线的路线中,每个系统设备产生的噪声都将被带入供电线路中并影响到其他的系统设备。而电源位面系统中,电流分布在整个层上。由于整体阻抗小,电源位面系统产生的噪声比总线系统的更小。

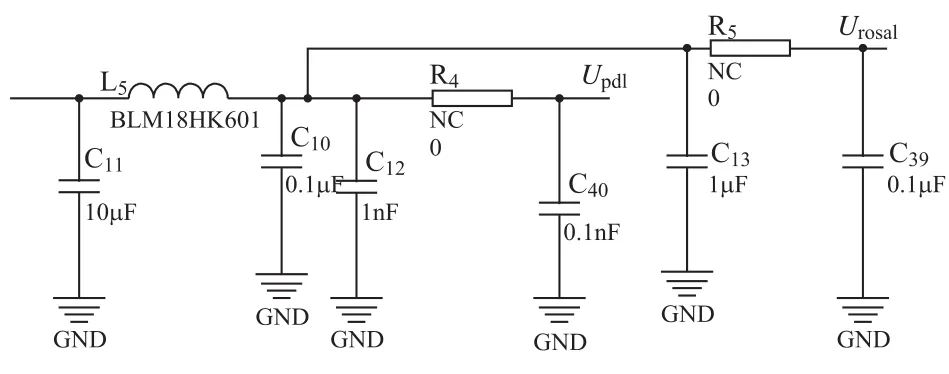

仅仅靠电源分配系统是无法减小系统设备产生的噪声。不论使用怎样的电源分配方案,整个系统都会产生噪声,因此需要额外的过滤措施,例如滤波电容。一般来说,在系统的电源接入端放一个1μF~10μF的电容。在高频环境下工作的有源器件,往往有一个以上的电源引脚,这个时候一定要注意在每个电源的引脚附近设置单独的去耦电容,容值在100 nF左右。在电路板空间允许的情况下,建议每个引脚使用两个去偶电容,容值分别为1 nF和100 nF。一般使用材质为X5R或者X7R的陶瓷电容。选择在高频环境下工作的元器件时,尽可能使用表贴0402器件,因为表贴元件一般体积小,元件的引脚很短。这样可以尽可能减少元件引脚和元件内部走线带来的附加参数的影响。尤其是分立的电阻、电容、电感元件,使用较小的封装有利于提高电路的稳定性和一致性。例如,对于同一个有源器件,不同的电源引脚可能为这个器件(芯片)中不同的功能模块供电,而芯片中的各个功能模块可工作在不同的频率上。为了防止不同器件之间产生的噪声互相干扰,在有源器件的每个功能模块的供电引脚除了采用单独的去耦电容外,最好再添加一个电感磁珠(10μH左右),消除线路噪声,同时防止器件产生的噪声串到线路上相互干扰。如图2所示,在电源附近都添加了电容,电源电路上添加了电感磁珠,电容离电源越近,电容的滤波效果就越好。

图2 π型滤波电路

6 结 语

高频电路随着信号频率的提升,信号的波长不断减小。当信号波长减小到可以与电路板传输线长度相比拟时,高速PCB信号将面临信号的过冲、下冲、振铃、延迟和单调性等问题。与此同时,当高速信号传输时,PCB板上电源层与地层间的电压在PCB板的各处都不尽相同,从而影响到IC芯片的供电,导致芯片的逻辑错误。

为了保证高速器件的正确工作,电路设计时应该保证信号的完整性,消除电压的波动,保持低阻抗的电源分配路径。本文从叠层设计、阻抗匹配与端接、走线设计、电源设计、过孔设计等五个方面,理论结合实际,提出了对高速电路设计处理的方法,对于高速PCB电路设计有一定的借鉴意义。

[1]周润景.Cadence PCB设计与制板[M].北京:电子工业出版社,2005.

[2]Dougl Brooks.信号完整性问题和印制电路板设计[M].北京:机械工业出版社,2005.

[3]夏 凡.高速数字电路中的信号完整性设计[D].南京:南京理工大学,2006.

[4]侯莹莹,关丹丹.高速PCB中的过孔设计研究[J].电子与封装,2009,9(08):20-22.

[5]王海秀.基于DSP的无陀螺捷联惯导系统的硬件设计[D].哈尔滨:哈尔滨工程大学,2007.