面向三维集成电路版图设计的EDA插件研究*

2015-02-23竺兴妹段倩妮南京工程高等职业学校电子工程系南京35南京航空航天大学电子信息工程学院南京006

陈 娟,竺兴妹,段倩妮(.南京工程高等职业学校电子工程系,南京35; .南京航空航天大学电子信息工程学院,南京006)

面向三维集成电路版图设计的EDA插件研究*

陈娟1*,竺兴妹1,段倩妮2

(1.南京工程高等职业学校电子工程系,南京211135; 2.南京航空航天大学电子信息工程学院,南京210016)

摘要:为了更好的满足工程师在三维集成电路设计中的需要,基于SKILL语言,对业界主流版图设计工具Cadence Virtuoso进行二次开发,开发出能辅助三维集成电路设计的EDA插件。该EDA插件主要包括3种功能:自动对齐,自动打孔和三维可视化技术。最终在三维集成电路的背景下设计两个并联的反相器以验证算法功能。实验表明,该EDA插件能够满足三维集成电路设计的需求,简化三维集成电路版图设计的过程,具有很好的易用性。

关键词:三维集成电路;插件; SKILL;硅穿孔;版图设计

随着晶体管加工工艺的不断进步,按比例缩小集成电路的发展思路已经接近极限,面临的问题有:(1)未来系统需要集成多种非电子元件,如射频、光/光电、执行器、MSMS等; (2)互联线延迟对电路性能影响的比例不断提升[1]。正是这一系列的严峻挑战促使了“More Than Moore”定律的发展与应用[2-3]。国际半导体技术蓝图宣称三维集成电路是达到更高晶体管集成密度的关键技术之一[4]。该项技术可以在芯片面积不变的前提下进一步提升芯片的集成度。此外,三维集成电路更注重系统集成和各种工艺的兼容性,这有利于提升微电子系统的性能[5-7]。但是,现阶段的EDA软件如Cadence等仅仅支持三维集成电路版图的设计规则检查(DRC)、版图原理图检查(LVS)和版图仿真,没有覆盖整个三维集成电路设计流程,造成了目前工程师设计三维集成电路时过程复杂,且容易出错[8]。

为了更好的满足工程师在三维集成电路设计中的需要,本文在下面第1部分研究了三维集成电路的物理实现流程,并在第2部分内容中基于现有三维集成电路版图设计流程的问题,构建三维集成电路的设计流程;第3部分基于SKILL语言[9-11],对Cadence Virtuoso进行二次开发,开发出能辅助三维集成电路设计的EDA插件。第4部分设计了一个设计实例对算法功能进行了验证。

1 三维集成电路的物理实现流程

三维集成电路被定义为一种系统级集成结构,在这一结构中,多层平面器件被堆叠起来,并经由硅穿孔TSV(Through Si Via)在Z方向连接起来[12]。为制造这样的叠层结构,TSV制作、层减薄技术、对准和键合技术是三维集成电路制造的3大关键技术。

TSV制作:Z轴互连是穿透衬底(硅或者其他半导体材料)的连接,TSV的尺寸取决于TSV的高度,TSV的高度越高,TSV的尺寸越大; TSV可堆栈多片芯片,其设计概念来自于印刷电路板,在芯片钻出小洞(制程又可分为先钻孔以及后钻孔两种),从底部填充入金属,硅晶圆上以刻蚀或镭射方式钻孔,再以导电材料如铜、多晶硅、钨等物质填满。

层减薄技术:初步应用需减薄到大约75 μm~50 μm,而在将来需减薄到约25 μm~1 μm。

对准和键合技术:芯片与晶圆(D2W)之间,或者晶圆与晶圆(W2W)之间,将TSV对准并键合。

基于上述关键技术,三维集成电路的物理实现流程根据钻孔的次序,分为先钻孔流程和后钻孔流程。

先钻孔流程包括如下步骤:

(1)基于光刻,掺杂和刻蚀工艺实现第1层集成电路的晶体管及其相应金属层。

(2)生长第2层集成电路的衬底。

(3)通过TSV制作工艺,生成第1层和第2层集成电路之间的TSV。

(4)再基于光刻,掺杂和刻蚀工艺生长第2层集成电路的晶体管及其相应金属层。

由于工艺水平的限制,上述流程中的第2步骤并不成熟,因此先钻孔流程的三维集成电路良片率较低。目前三维集成电路的物理实现主要依赖第2种后钻孔流程,其流程包括如下步骤:

(1)基于光刻,掺杂和刻蚀工艺分别实现第1层和第2层集成电路的晶体管及其相应金属层。

(2)基于层减薄技术减薄第2层集成电路的衬底。

(3)通过TSV制作工艺,生成第1层和第2层集成电路之间的TSV。

(4)对第2层集成电路中的TSV上方进行淀积绝缘层。

2 三维集成电路(IC)版图设计流程

2.1三维IC版图特点

由第2章介绍可知,三维集成电路可以视作由若干层二维集成电路组成,这些二维集成电路在Z轴方向上通过TSV工艺进行连接。因此三维集成电路的版图可以视为若干个二维集成电路版图的集合。值得指出的是,三维集成电路中的多层二维集成电路彼此之间存在电气连接关系;即使没有电气连接,也会因为彼此临近,会对相邻的电路性能产生影响。因此,三维集成电路的版图设计过程相对于二维集成电路版图设计过程,会更加复杂。

2.2现有三维IC版图设计流程的问题

由于三维集成电路中的多层二维集成电路彼此之间存在电气连接关系,因此在二维集成电路设计EDA工具Cadence Virtuoso中实现上述步骤,主要存在的问题有:

(1)三维集成电路版图中,各层之间的相对位置必须非常精确,丝毫不差。

(2)各层集成电路对相邻层的电路会有性能影响,因此在布局时需要考虑彼此的位置和方向。

(3)三维集成电路设计中,各层之间需要增加TSV过孔。而各层电路存放于不同的CellView中,对于一个TSV,需要手动分别在两个不同CellView中增加TSV,且要保证TSV的位置严格对应。

2.3本文提出的三维IC版图设计流程

为了解决上述问题,本文结合二维集成电路设计流程,提出一种适合三维集成电路的版图设计过程。其设计过程包括如下步骤:

(1)实现基本单元版图。新建不同的CellView文件,实现版图所需的基本单元版图。

(2)布局。通过调用单元电路,根据设计需求,使这些单元分布在三维集成电路版图中。在布局过程中,往往需要综合考虑上下层电路彼此之间的关系。

(3)布线。通过对这些单元进行连线,对于不同层的金属连线还需要增加TSV,使其成为一个完整的三维集成电路的版图。在布线过程中,需要在相连的两层版图中都要打上TSV,并且两者位置需要完全吻合对应。

3 本文提出的三维IC版图插件设计

在2.3节所述的三维集成电路设计流程中,步骤(1)内容是和二维集成电路版图设计内容完全一致。但是步骤2和步骤3的内容是三维集成电路版图设计中特有的。为了方便设计者在步骤2和步骤3中的版图设计,本文提出一种EDA插件。该插件包括3种功能:自动对齐,自动打孔和三维可视化。

以在三维集成电路工艺环境下设计两个并联的反相器为例,其步骤主要有如下3步。

(1)在两个版图文件上分别画上两个反相器的版图。

(2)摆放反相器的位置。这期间,可以通过三维可视化观察各层电路版图的相对位置。

(3)在相邻层之间绘制TSV时,只要在一层中绘制TSV,运行自动打孔功能后,插件会在相邻层对应的位置绘制TSV。

(4)在绘制版图过程中,若移动了其中一层版图。为使另一层版图与之依旧对齐,可以运行自动对齐功能的脚本完成移动另一层版图的功能。当完成自动对齐功能后,还可以运行可视化功能,观察脚本是否运行正确。

3.1自动对齐

自动对齐是当三维集成电路版图中的任意层版图被移动后,运行该脚本,相邻版图会对应移动,使得相邻版图的相对距离不变,以保证相邻版图之间的TSV连接正确。

为实现上述功能,本文提出的自动对齐算法首先在相邻版图之间寻找对应点,一般取有电气连接关系的TSV作为对应点;然后通过对应点,分别读取相邻版图的位置,计算相邻版图的坐标偏移量;最后根据计算的坐标偏移量,移动相邻版图实现对齐。

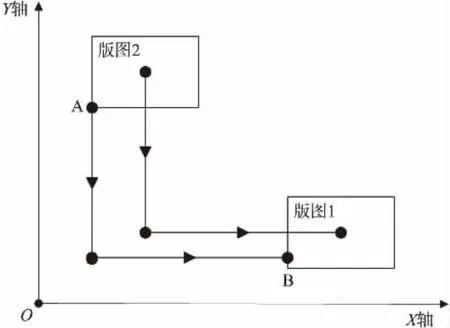

图1中用两个长方形标识相邻的版图1和版图2。如图所示,版图2中内部任意点移动到版图1中相应点位置,其在X轴方向上的移动距离、Y轴上的移动距离,与版图边框上点移到对应点的移动距离是完全一致的。因此,若将版图2移动到版图1的位置,只需要计算出相邻版图对应点在X轴和Y轴的偏移量。

图1 自动对齐核心算法说明图

因此,通过对对应点的提取可以得到点A的坐标(a,b),同样的可以得到点B的坐标(c,d)。

基于式(1)和式(2),可得到移动版图2到版图1所需的偏移量,然后调用系统自带函数即可移动版图2中的所有图形。

3.2自动打孔

TSV是相邻层电气连接的桥梁,若相邻层的TSV位置错位,则会对电路性能带来致命影响。例如,若相邻版图的TSV只有部分对齐,会导致TSV的电阻增大。如果两层版图的TSV完全分离,这会导致相邻版图没有电气连接关系,是完全错误的打孔。

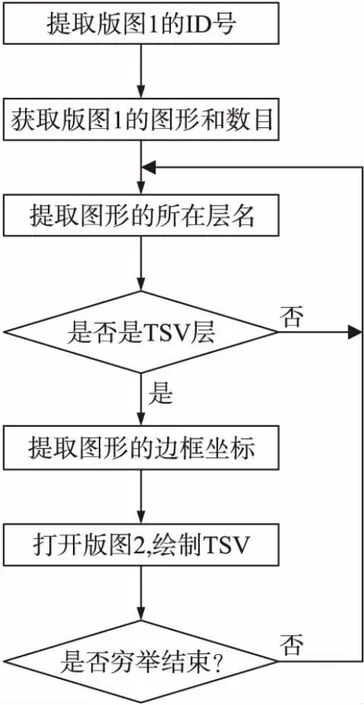

为避免绘错TSV的位置,本文提出自动打孔功能。当在一层版图上绘制TSV后,运行自动打孔功能后,会在相邻版图上绘制对应的TSV版图,其算法流程如图2所示。

图2 自动打孔算法流程图

3.3三维可视化

为了方便对比相邻版图之间的关系,同时省去电路设计时的麻烦,本文设计了三维可视化功能。设计者可以通过该功能在任意层版图中观察相邻版图的情况。

可延续的抽象规则与制度理念组成高校制度文化的第三层面——价值观念层,它是在高校的长期发展过程中,因为高校全员的习惯、经验、知识积累等自然形成的,是高校精神文化的核心,反映并决定着高校的集体意志与价值取向。由于这种价值观念已形成了相对稳定的影响力且这种影响力具有延伸性和扩展性,其便具有了作为“制度”的“强制性”,在一定程度上引导、校正高校物质文化和精神文化的价值变迁。

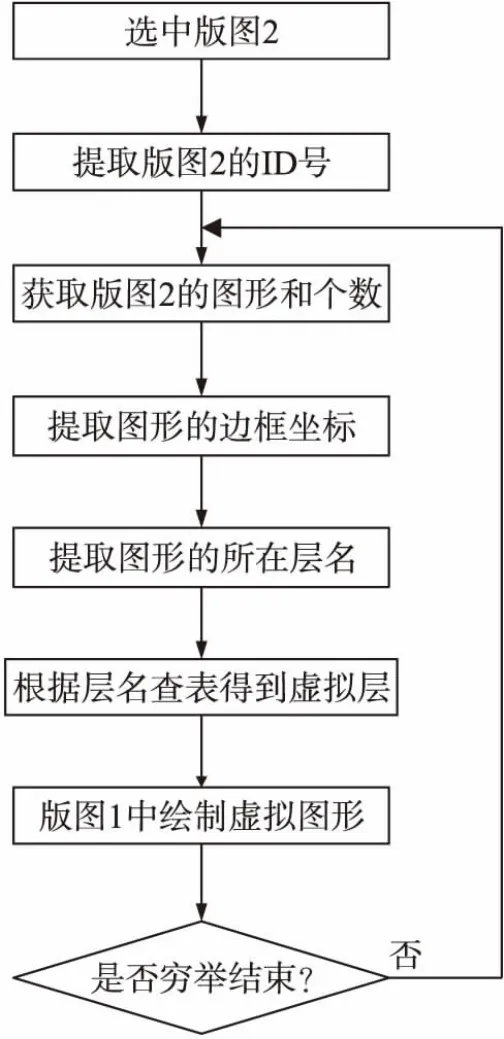

三维可视化由两个模块组成:可视化模块和删除虚拟版图模块。例如,当需要在版图1中观察版图2的相对位置时,可以运行可视化模块;对比完后,再运行删除虚拟版图模块,删除可视化模块产生的供观察用的虚拟版图,具体的算法和调用流程如图3所示。

图3 三维可视化技术部分流程图

4 设计实例

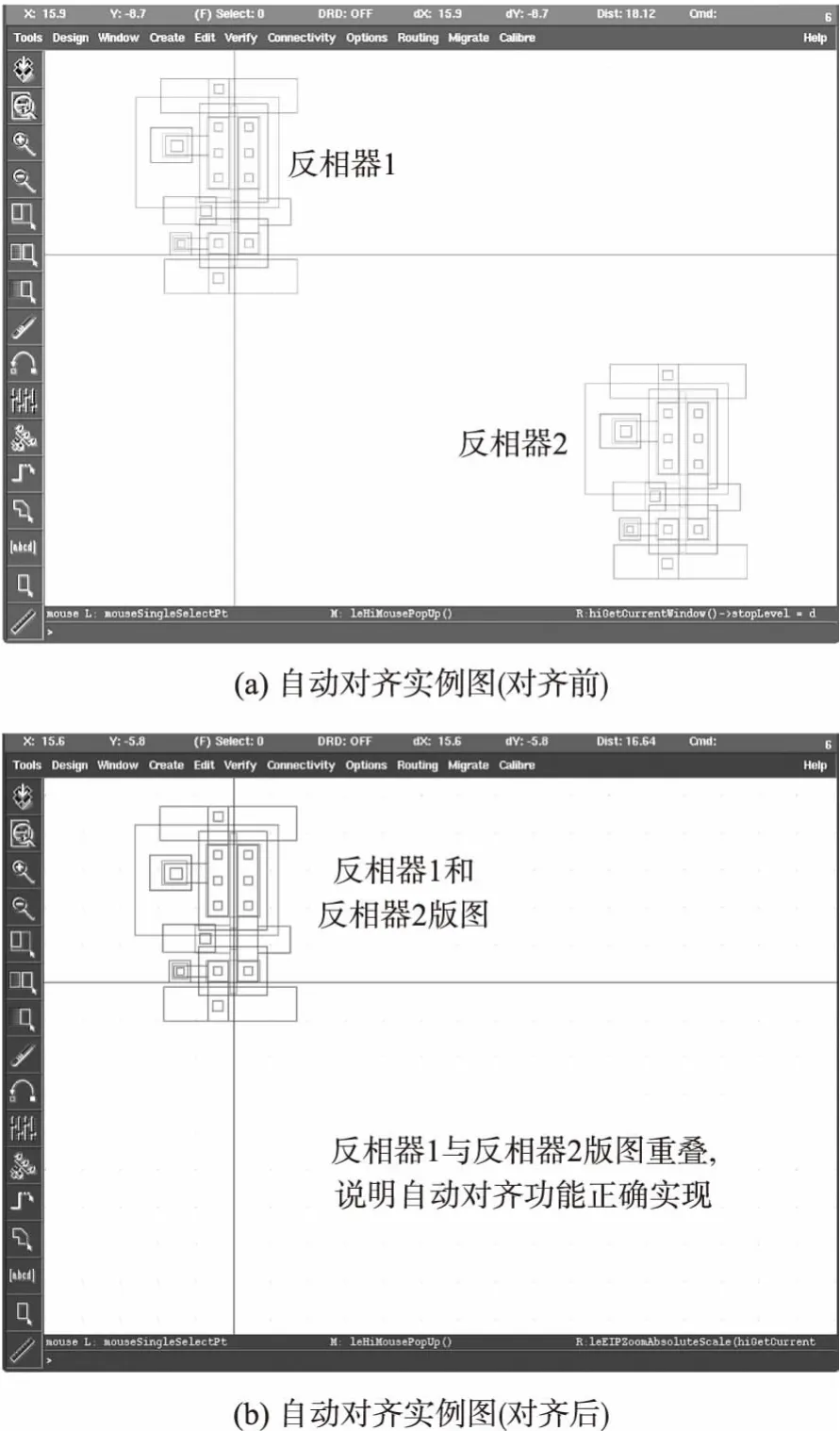

为验证所提插件的正确性和实用性,本文在三维集成电路工艺背景下设计了两个并联的反相器。在设计实例中,这两个反相器分别被命名为反相器1和反相器2,并且在三维集成电路中分别处于两个相邻版图中。本文针对反相器1和反相器2版图,依次运行自动对齐、自动打孔和三维可视化脚本,并通过观察运行结果判断脚本的准确性。

4.1自动对齐

图4所示的是自动对齐实例图。如图4(a)所示,分别绘制了反相器1和反相器2版图。当运行脚本后,反相器2版图被整体移动和反相器1版图重合,对齐后的版图效果如图4(b)所示。

图4 反相器实例图

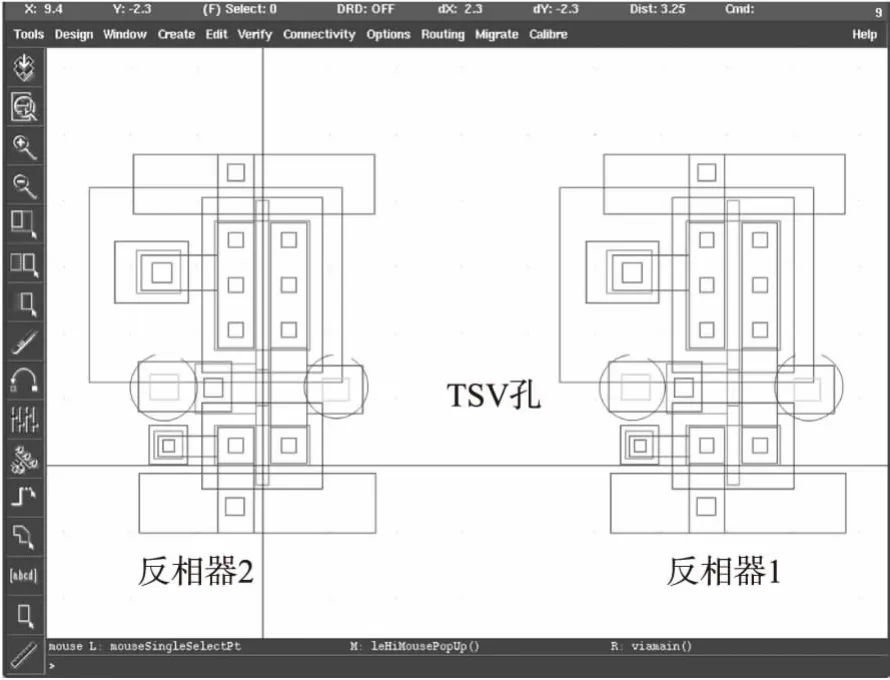

4.2自动打孔

图5所示是自动打孔功能运行后的示意图。为了方便观察自动打孔的效果,反相器1和反相器2版图被手动分开。如图5所示,反相器1和反相器2的TSV位置分别和版图其他图形的相对关系是完全一致的,说明自动打孔的功能是正确的。

图5 自动打孔实例图

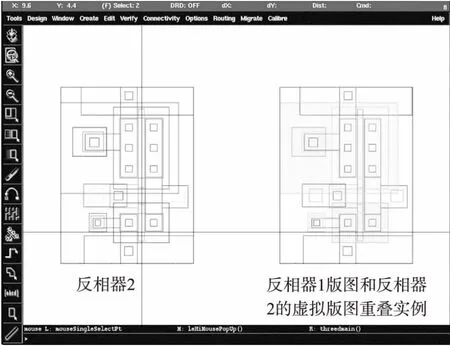

4.3三维可视化

图6 三维可视化实例图

5 总结

为了更好的满足工程师在三维集成电路版图设计中的需要,本文基于业界主流二维集成电路版图设计工具Cadence Virtuoso,构建三维集成电路的版图设计流程;并基于SKILL语言,对Cadence Virtuoso进行二次开发,开发出能辅助三维集成电路版图设计的EDA插件。该EDA插件主要包括3种功能:自动对齐,自动打孔和三维可视化技术。为了验证该EDA插件在三维集成电路设计中的易用性和实用性,本文在三维集成电路工艺背景下设计两个并联的反相器。实验表明,该EDA插件简化了三维集成电路版图设计过程,具有很好的易用性。

参考文献:

[1]郑伟,李文钧,刘军,孙玲玲.基于90 nm低功耗NMOS工艺射频器件的版图优化[J].电子器件,2011,34(6),645-648.

[2]Wristers D.Complex Trade-Offs-Enablement of Moore and More Than Moore[C]//2013 International Conference on IC Design and Technology,2013:1-2.

[3]Heinig A,Dietrich M,Herkersdorf A,et al.System Integration—The Bridge between More Than Moore and More Moore,Design [C]//2014 Automation and Test in Europe Conference and Exhibition(DATE),2014:1-9.

[4]Hui Min Lee,En-Xiao Liu,Er-Ping Li,et al.Impact of Technology Scaling on Electrical Characteristics of Through-Silicon Via Correlated with Equivalent Circuits[C]//EMC Europe 2011 York,2011,339-344.

[5]Qian Libo,Zhu Zhangming,Yang Yintang.System Level Performance Evaluation of Three-Dimensional Integrated Circuit[C]//2011 IEEE 9th International Conference on ASIC (ASICON),2011:694-697.

[6]Chen K N,Tan C S.Integration Schemes and Enabling Technologies for Three-Dimensional Integrated Circuits[J].IET Computers and Digital Techniques,2011,5(3),160-168.

[7]夏艳.3D集成的发展现状与趋势[J].中国集成电路,2011,146(7):23-28.

[8]Chang-Hsin Cheng,Chung-Kai Liu,Hsing-Chuang Liu,et al.On-Line Error Detection and Correction Techniques for TSV in Three-Dimensional Integrated Circuit[C]//2011 International Symposium on Intelligent Signal Processing and Communications Systems(ISPACS),2011,1-5.

[9]毕宗军,罗岚,杨军.基于SKILL语言的按比例自动缩放版图方法[J].电子器件,2006,29(4):1187-1191.

[10]马亮.基于VC的Cadence二次开发[J].电子科技,2011,24(2):98-101.

[11]赵兵,黄凯,杨军.基于SKILL语言的自动天线效应修复器设计[J].微电子学,2008,38(2):182-186.

[12]Civale Y,Redolfi A,Jaenen P,et al.Through-Silicon Via Technology for Three-Dimensional Integrated Circuit Manufacturing[C]//2012 35th IEEE/CPMT International Electronic Manufacturing Technology Symposium(IEMT),2012:1-5.

陈 娟(1983-),女,汉,江苏丹阳,南京工程高等职业学校电子工程系讲师,电路与系统,cherry_c_j@163.com;

段倩妮(1990-),女,汉,江苏常州,南京航空航天大学研究生,集成电路设计,qianniduan@163.com。

竺兴妹(1975-),女,汉,江苏南京,南京高等职业学校电子工程系副教授,电气自动化及其自动化技术,472036640 @qq.com;

A System-Level Post-Simulation Verification Platform for Mixed-Signal SoC*

HU Xiaogang1,ZHAO Linna1,YU Zhiguo1*,WEI Jinghe2,GU Xiaofeng1

(1.Key Laboratory of Advanced Process Control for Light Industry(Ministry of Education),Department of Electronic Engineering,Jiangnan University,Wuxi Jiangsu 214122,China;

2.The 58th Research Institute of China Electronics Technology Group Corp,Wuxi Jiangsu 214035,China)

Abstract:Regarding the problem of slow post-simulation speed of the large-scale mixed-signal System-on-Chip (SoC),a system-level post-simulation verification platform for mixed-signal SoC is proposed.Based on the traditional Verilog-cdl post-simulation verification platform and popular EDA tools,the proposed platform utilizes a Verilog-cdl-Verilog simulation method in which the modules with long simulation time are replaced by the Verilog ones.As a result,the verification process is obviously fastened.The design flow of the simulation platform is described in details,including the verification environment setup,the system script design and the mixed-signal simulation interface design.The instruction set simulation based on the verification platform is tested and verified.The results indicate that the verification platform is feasible and reliable,which can shorten the developing period of large-scale mixed-signal SoC.

Key words:mixed signal SoC; post-simulation; Verilog-cdl-Verilog; verification platform

doi:EEACC:257010.3969/j.issn.1005-9490.2015.04.008

收稿日期:2014-10-17修改日期:2014-11-11

中图分类号:TN402

文献标识码:A

文章编号:1005-9490(2015)04-0749-05

项目来源:国家自然科学基金项目(61106029)