CMOS工艺X射线图像传感器设计

2014-08-07孟丽娅王庆祥

孟丽娅,袁 松,王庆祥

(1.光电技术及系统教育部重点实验室,重庆 400032;2.重庆大学 光电工程学院,重庆 400032)

X射线在医学成像、生物分子结构研究、空间应用、工业产品质量检查和评估等方面具有广泛、重要的应用。常规的高精度X射线数字化成像技术通常需采用CsI(Tl)闪烁体或Gd2O2S增感屏将X射线转换为可见绿光或蓝光[1],然后通过光纤或透镜系统,经CCD或CMOS图像传感器将该荧光信号变换为电信号从而获得图像,而闪烁体或增感屏会降低成像信号的空间分辨率和时间分辨率。若能省略闪烁体或增感屏,直接对X射线进行数字成像,有望进一步提高X射线成像检测系统的分辨率和探测效率[2]。本文研究一种不需中间光转换层,直接对X射线进行成像的低成本标准CMOS工艺图像传感器,设计该种图像传感器的像元结构,对其X射线探测原理进行理论分析,并采用0.5 μm标准CMOS工艺制作含不同光敏元的线阵图像传感器,进行X射线探测实验。

1 像元结构

光敏元采用N阱/P衬底二极管结构,像元内电路为典型的3-T读出结构[3],像元内晶体管采用N型MOS晶体管以避免影响光敏元对电荷的收集。X射线对N型MOS晶体管器件的影响主要为阈值电压漂移和漏电流的增加[4],可采用环形栅结构进行辐射加固[5]。X射线入射到硅电路上,将穿透制作在硅表面上的电路结构,沿着射线穿过的轨迹按一定比例损失能量,并在硅材料中引起电离辐射效应,激发出电子/空穴对,激发出的电子一部分在扩散过程中与空穴复合,另一部分到达N阱被收集。在低载流子密度情况下,决定非平衡载流子寿命的主要复合机制是借助于缺陷能级的间接复合[6]。

当X射线持续入射到探测器中,单位时间内在每μm硅衬底中激发的电子/空穴对数目n为:

n=C1ρDX/Eg

(1)

式中:C1为每μm硅衬底所吸收的X射线能量的比率;DX为单位时间内X射线剂量;Eg为硅中电子/空穴对的电离能;ρ为探测器材料的密度。

施加了正偏压的N阱将不断吸引被激发出来的电子,N阱深度越大,吸引的电子数目越多。若电荷载流子的产生寿命为τ′,则持续的X射线入射不断地产生电子/空穴对,所生成的额外载流子的密度N(t)为:

N(t)=nτ′(1-et/τ′)=C1ρDXτ′(1-et/τ′)/Eg

(2)

(3)

电子速度ve为:

(4)

式中:E为电场强度;Ec=vs/μ,vs为电子漂移饱和速度。

在300 K时,μ=1 450 cm2/(V·s),β=1.30,Ec=7 240 V/cm,则单位时间内收集的电荷总数为:

Q=N(t)s=C1ρDXτ′(1-et/τ′)·

(5)

电荷形成的电压VX=Q/CT,二极管势垒电容CT为:

(6)

式中:ε为相对介电常数;ε0为真空介电常数;NA为P区掺杂浓度;q为电子电荷;V为外加电压;Vbi为硅的内建电势。

则有:

(7)

由式(7)可知,光敏元面积越小、衬底的掺杂浓度越低、衬底缺陷越少、施加的偏压越大,VX越大。另外,在同一像元中有多个光敏元有利于更好地收集X射线在衬底上激发的电子,但随光敏元个数的增加,其寄生电容和漏电流也将增大。本文设计了4种像元:单个像元内含1、2、3及4个光敏元,每个光敏元面积均为5 μm×5 μm,像元内的光敏元的水平中心距为25 μm,垂直中心距为30 μm,相对位置如图1所示。

X射线对光敏元的影响主要体现为漏电流的增大[7],光敏元漏电流增大的原因是对光敏元进行隔离的场氧具有较栅氧更多的缺陷,更易捕获电荷从而导致电荷的堆积,因此在光敏元边缘处利用多晶硅层在N阱的边缘处形成较薄的栅氧,减少捕获电荷[8],但在栅氧和场氧的交界处会形成寄生的边缘N型场效应晶体管,该寄生场效应晶体管同样具有阈值电压漂移特性,这样在寄生晶体管的栅极电压为0 V时可能会有源漏电流,因此,采用P+保护环以避免该源漏电流的产生。

图1 4种光敏元结构

2 X射线实验

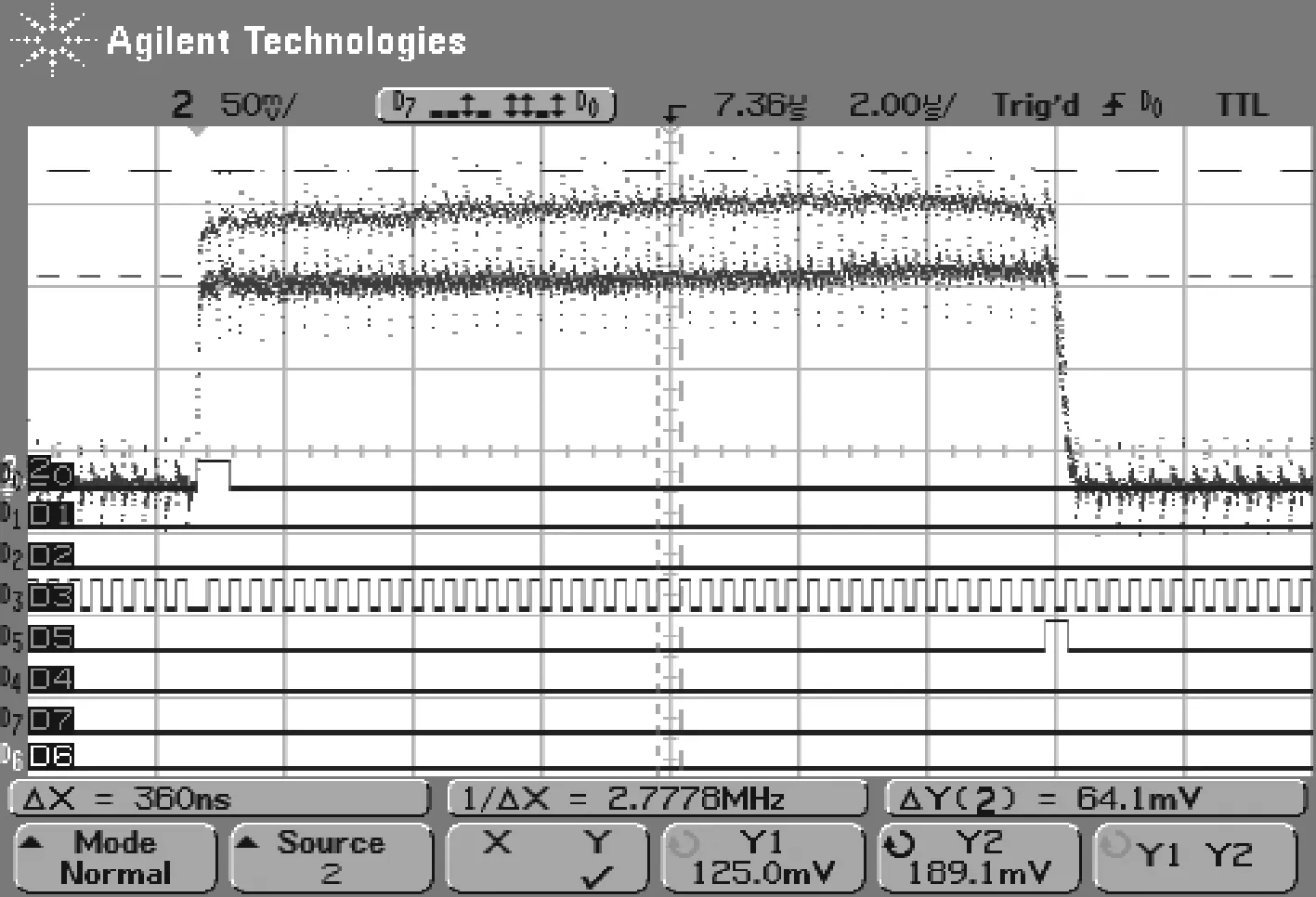

本文采用0.5 μm DPTM CMOS工艺制作了40位线阵,比较不同结构像元的电荷收集效果。流片封装后的40位线阵由40位光敏元、源随器、相关双采样电路和输出缓冲器及移位寄存器[9]组成。该线阵中像元结构依次为1、2、3和4个光敏元结构,每种类型设计了10位像元,中心距100 μm。图2为示波器记录的对牙科射线仪的输出响应,由于牙科射线仪为整流输出,并不是恒定直流射线源,而线阵的积分时间很短,因此示波器上出现高低不同的多条曲线。

图2 线阵在牙科射线仪照射下的输出

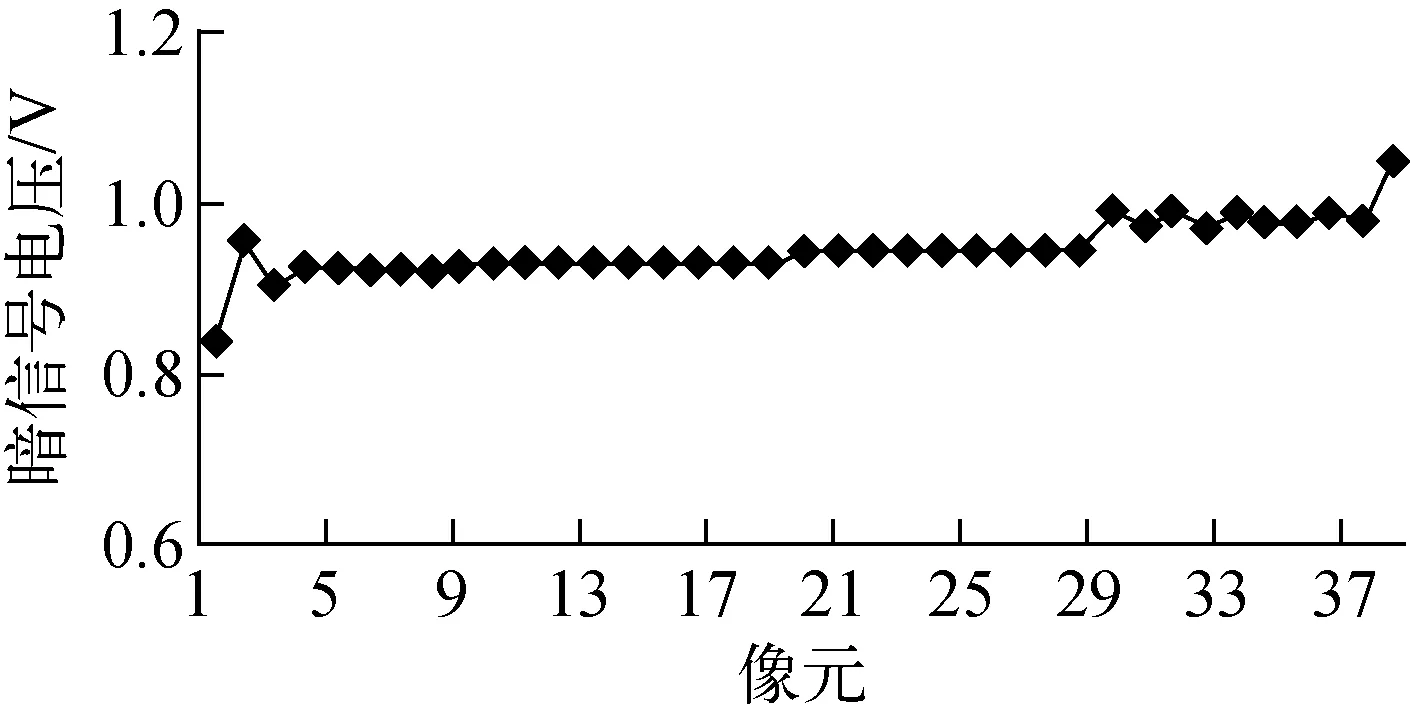

利用NI数据采集卡PCI 6115和LabView虚拟仪器程序及SB-80-250直流X射线源对该线阵进行测试,采用厚0.12 mm的铝片将实验用线阵的窗口进行高频压焊密封。SB-80-250直流X射线源的管电流范围为10~250 μA,管电压范围为35~80 kV。本文分别测试3片线阵样管在无入射光时的暗信号电压及在不同射线源输出下的电压响应曲线(积分时间tint=18.7 ms),结果示于图3~5。图3~5中所有数据均为测试100次的均值(图中未显示第1位像元的输出)。图3为无X射线照射时测得的线阵暗信号电压Vod,含1个光敏元的像元暗信号电压均值为0.914 V,含2个光敏元的像元暗信号电压均值为0.929 V,含3个光敏元的像元暗信号电压均值为0.945 V,含4个光敏元的像元暗信号电压均值为0.990 V。暗信号电压随像元中光敏元个数的增加而增大,总的漏电流随光敏元个数的增加而增大。

图3 线阵输出暗信号电压

图4为将X射线源的管电流固定为250 μA,改变其管电压时线阵的有效输出电压Voe(Voe为线阵各像元的输出电压减去相应的暗信号电压)。可看出,当X射线源管电压为75 kV以上时,线阵输出已基本饱和,饱和有效输出电压约为1.4 V。

图4 线阵在不同管电压X射线源下的有效输出电压

图5为将X射线源管电压固定为80 kV,改变其管电流时线阵的有效输出电压。可看出,当X射线源管电流为200 μA时阵列输出未饱和,而增大X射线源管电流至250 μA时阵列输出饱和。

图5 线阵在不同管电流X射线源下的有效输出电压

由图4和5可见,对于含1个光敏元、2个光敏元和3个光敏元的像元结构,随着光敏元个数的增加有效输出电压增大;但对于含4个光敏元的像元结构,有效输出电压低于2个光敏元和3个光敏元的像元结构,这是因为像元的总寄生电容和漏电流随光敏元个数增加的结果。

3 结论

本文设计了用于X射线直接成像的图像传感器线阵,分析了其电荷收集的原理,设计了含多个光敏元的辐射加固像元结构。采用虚拟仪器技术对该线阵进行了测试,该线阵的暗信号电压约为1 V,饱和输出电压约为2.4 V。在单个像元内设计多个光敏元有利于电荷的收集,但随着光敏元个数的增加寄生电容和漏电流增加,针对本文所设计的光敏元结构及所采用的工艺,单个像元内含3个光敏元的结构得到的有效输出电压最大。

参考文献:

[1] XIAO Bowen, SUN Chengwei, CHEN Hengyin, et al. A digital radiography readout system for low dose and high resolution amplified pixel sensor[C]. Taipei: IEEE, 2012.

[3] DULINSKI W, BERST J D, BESSON A, et al. CMOS monolithic active pixel sensors for minimum ionizing particle tracking using non-epitaxial silicon substrate[J]. IEEE Transactions on Nuclear Science, 2004, 51(4): 1 613-1 617.

[4] 李冬梅,皇甫丽英,王志华,等. 不同设计参数MOS器件的γ射线总剂量效应[J]. 原子能科学技术,2007,41(5):522-526.

LI Dongmei, HUANGFU Liying, WANG Zhihua, et al. γ-radiation total dose effects of different sized MOS devices[J]. Atomic Energy Science and Technology, 2007, 41(5): 522-526(in Chinese).

[5] 范雪,李威,李平,等. 基于环形栅和半环形栅N沟道金属氧化物半导体晶体管的总剂量辐射效应研究[J]. 物理学报,2012,61(1):016106.

FAN Xue, LI Wei, LI Ping, et al. Total ionizing dose effects on N-channel metal oxide semiconductor transistors with annular-gate and ring-gate layouts[J]. Acta Phys Sin, 2012, 61(1): 016106(in Chinese).

[6] 曹建忠. 半导体材料的辐射效应[M]. 北京:科学出版社,1993:69-80.

[7] SAYED I E, TONY Y C, ERIC R F, et al. Design of radiation hard CMOS APS image sensors in a 0.35-μm standard process[J]. SPIE Proceedings, 2001, 4306: 50-59.

[8] LEO H C B, SUZANA D, MILTON F R, Jr, et al. Layout techniques for radiation hardening of standard CMOS active pixel sensors[J]. Analog Integrated Circuits and Signal Processing, 2008, 57(1-2): 129-139.

[9] 孟丽娅,刘泽东,胡大江,等. CMOS APS用移位寄存器抗SEU加固方法[J]. 原子能科学技术,2012,46(增刊):577-581.

MENG Liya, LIU Zedong, HU Dajiang, et al. SEU-hardened design for shift register in CMOS APS[J]. Atomic Energy Science and Technology, 2012, 46(Suppl.): 577-581(in Chinese).