基于FPGA的异步流水乘法器设计的教学方案

2014-04-26李贞妮李晶皎金硕巍

李贞妮,李晶皎,金硕巍

(东北大学信息科学与工程学院,辽宁沈阳 110819)

0 引言

随着集成电路规模的不断增大,同步电路中的功耗和时钟偏移等问题日趋严重。与同步电路相比,异步电路具有无时钟偏移、模块化程度高、功耗低以及电磁兼容性强等优势,越来越受到广泛关注[1]。异步电路也成为未来集成电路发展的一个重要方向。因此,对于电子科学与技术专业的学生来说,学习异步电路设计方法十分必要,该部分内容已被纳入到“专用集成电路设计”课程的教学中。然而,异步电路设计比同步电路设计复杂得多,尚缺乏成熟的EDA设计工具的支持[2]。因此,在授课过程中,为了让学生能够尽快地掌握异步电路设计方法,设计出一个可以利用硬件描述语言在FPGA平台上实现的教学方案具有很重要的意义。

乘法器作为微处理器中不可或缺的组成部分,具有广泛的应用领域和巨大的使用价值,因此利用异步电路设计方法,设计并实现一款异步流水乘法器具有很大的实际意义。相应的设计教学方案可以帮助学生深入理解异步电路设计方法,掌握异步电路设计流程,并利用已有的开发工具实现并验证该异步电路系统。

1 教学方案的设计

1.1 异步乘法器实验系统设计

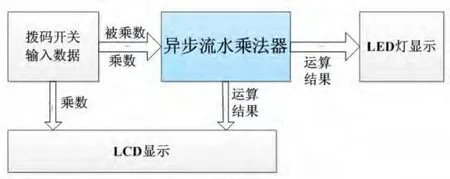

异步流水乘法器实验系统的FPGA设计教学方案如图1所示。其中,拨码开关实现被乘数和乘数的输入,被乘数和乘数通过异步乘法器运算后,使用LCD和LED同时显示乘法器运算的结果。在数据通路上,实现了4位任意数乘4位任意数的异步流水乘法器;在控制通路上则采用了两段握手协议,也即微流水线基本结构。

图1 异步流水乘法器的FPGA设计方案

1.2 异步乘法器总体设计

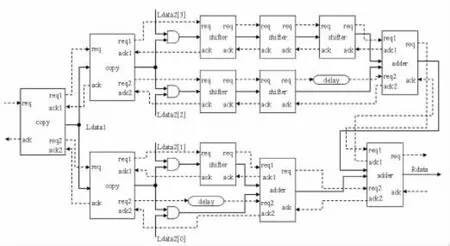

采用移位相加实现乘法器的基本功能。图2给出了异步流水乘法器功能实现的总体设计方案。其中,Ldata1为被乘数,Ldata2为乘数。

图2 异步流水乘法器总体设计图

该乘法器由信号分支模块copy、异步移位模块shifter、异步加法器模块adder以及延时模块delay组成。其中信号分支模块用来复制被乘数,并实现握手信号的分支。通过判断乘数的相应位是否为1,来决定是否通过异步移位模块对被乘数进行移位操作。异步加法器模块则是将移位后的数据进行相加,得到最终乘法的结果。图中的实线箭头表示数据流,而虚线箭头则表示信号流。

1.3 信号分支模块设计

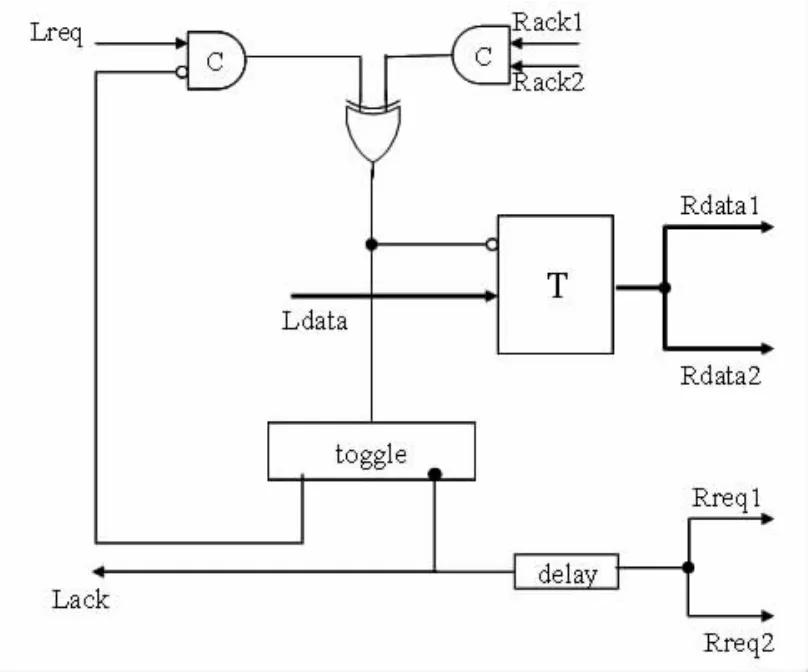

信号分支模块实现输入数据(被乘数)的复制,同时完成握手操作。我们以两段握手协议的电平敏感锁存器为设计基础,设计出信号分支模块电路图如图3所示。

图3 信号分支模块电路图

分支模块含有两个C单元,其中一个C单元完成握手过程,另一个C单元将输出通道上的多个应答信号合成为输入通道上的单元应答信号。将两个应答信号Rack1和Rack2合并,得到一个输入的应答信号。而输出的请求信号则直接一分为二,得到两个输出的请求信号,同时将输入的数据进行复制。

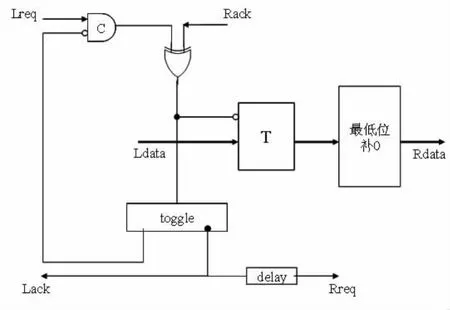

1.4 异步移位模块设计

移位操作是乘法器的关键步骤之一。作为异步电路中的功能模块,除了按指定的功能计算输入信号以外,它与相邻的锁存器间的握手也是透明的。图4为该异步乘法器所使用的移位模块结构,包括控制通路和数据通路。

图4 异步移位模块电路图

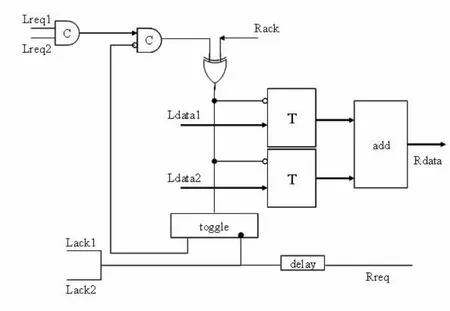

1.5 异步加法器设计

异步加法器是异步设计中一个最为基本的标准单元,本实验通过两段握手协议的方式来实现,电路图如图5所示。在该模块中,操作数通道和操作结果通道是分开的,即具有独立的输入和输出通道,这就意味着在输入端有汇合。两段握手协议的汇合同分支类似,也需要通过C单元,将输入通道上的多个请求信号合成为输出通道上的单个请求信号,而应答信号则直接一分为二。

该加法器可以实现两输入的数据相加,Lreq1和Leq2为两个请求信号,通过C单元汇合产生一个输入的请求信号。Lack1和Lack2则是一分为二的输出应答信号,这样就实现了一个两段握手协议的异步加法器。

图5 异步加法器电路图

2 FPGA实现及系统测试

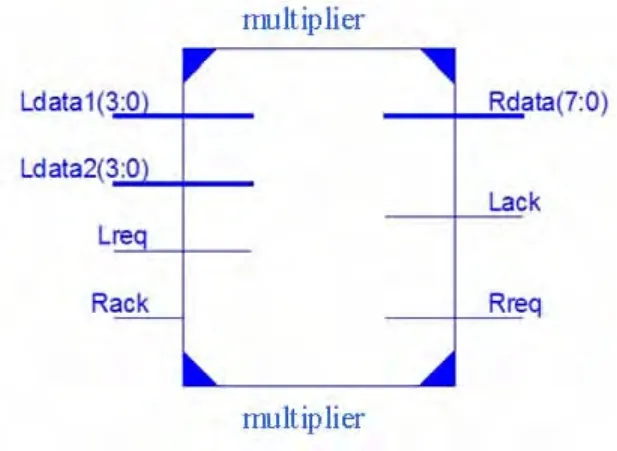

为了方便学生使用已有的工具,本教学方案设计采用Verilog硬件描述语言作为编程语言,ISE14.4作为编程环境,Modelsim SE 10.0a作为仿真工具,采用Xilinx公司的Genesys板卡作为目标硬件,在FPGA上实现并验证该异步流水乘法器。具体实现方法是分模块进行设计,将上述模块分别用硬件描述语言实现,最后组合成4位异步流水乘法器的顶层模块,见图6。

图6 异步流水乘法器顶层模块图

该模块可以实现两个四位任意数相乘的功能。Ldata1为4位的被乘数,Ldata2为4位的乘数,Lreq为上一模块输出的请求信号,Rack为下一模块输出的应答信号,Rdata为8位乘法结果数据,Lack为向上一模块输入的应答信号,Rreq为向下一模块输入的应答信号。当数据到来时,上一模块发出请求信号,即将Lreq跳转,此时该模块接收数据Ldata1[3:0]和Ldata2[3:0],并给上一模块发出相应的应答信号Lack,完成了一次握手过程。同时对下一模块发出数据请求信号Rreq。在进行乘法操作的过程中,将其中一个数据作为被乘数,另一个数据作为乘数,通过判断乘数的每一位是否为1,来对被乘数进行相应移位操作,并将最后移位的结果通过加法器进行相加,得到乘法结果。而由下一模块输出的应答信号Rack则在该模块输出数据时起作用。

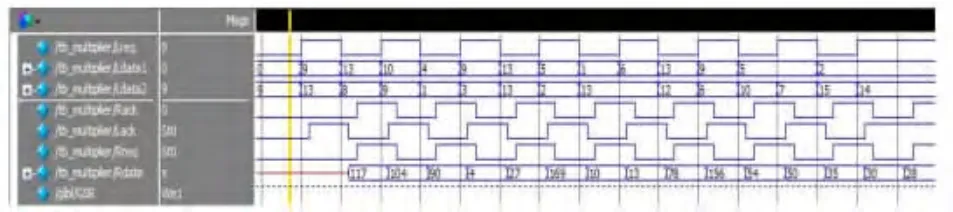

通过Modelsim仿真的波形图如图7所示。

图7 异步流水乘法器仿真波形图

通过仿真波形可以得到,Lreq翻转实现了数据发送请求,Lack的翻转代表获得乘法结果,从而实现了两段握手协议,且乘法器工作结果正确。进一步将异步流水乘法器的配置文件下载到Genesys板卡里,验证异步流水线乘法器系统功能的正确性,表明程序运行正确。

3 结语

本文提出了利用硬件描述语言在FPGA上设计并实现异步流水乘法器的设计教学方案。与使用Balsa和Petrify等专用异步电路设计工具相比,学生可以把主要精力放在异步电路设计方法的学习上,利用已经具备的硬件描述语言和FPGA初步开发能力,进行异步电路设计。这一教学方法符合本科生的教学特点,有助于学生加深对异步电路设计方法的理解与掌握。

[1]任洪广,石伟,王志英.异步集成电路设计方法综述[J].北京:计算机辅助设计与图形学学报,2011,23(3):543-552.

[2]赵不贿,徐雷钧,孙智权.异步电路设计原理-系统透视[M]北京:电子工业出版社,2009 1:1-5