高分辨率测距雷达系统宽带调制解调器*

2013-12-21张仁民钱莹晶

张仁民 ,钱莹晶,伍 清

(怀化学院物理与信息工程系,湖南 怀化418008)

测距分辨率是衡量随机码脉冲编码连续波相位调制雷达的主要参数指标之一,也是高分辨率成像雷达发展的核心问题[1]。根据雷达测距原理,要提高分辨率必须提高随机码的码速率——如想获得5 m 的分辨率必须将码速率设定在30 MHz,目前国内大多数该体制的雷达只能达到这一指标,而如想获得1 m 的分辨率必须将码速率提至150 MHz。

但150 MHz 速率的随机码脉冲编码雷达在设计和实现上具有一定的技术难度:其一,这个速率的码产生和传输均属于高速数字电路设计的范畴,会存在信号完整性问题SI;其二,为保证信号处理子系统在进行脉冲压缩时有足够的信噪比需要保证脉冲信号具有陡峭的动态时间和调制解调器的带宽。本文主要讨论第2 个问题,即高速随机码的传输和射频宽带调制解调器设计。

1 系统组成

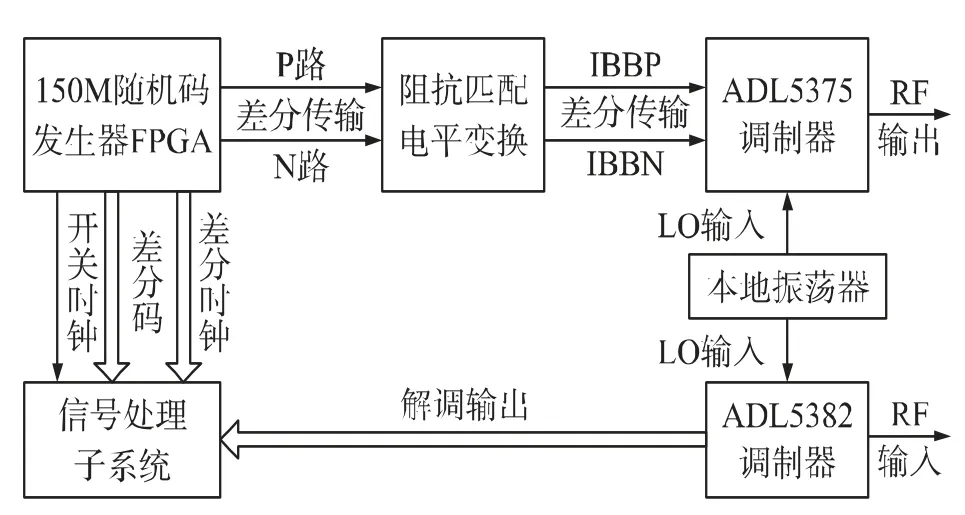

如图1 所示,本系统主要由基带信号发生器(码发生器)、射频调制和射频解调器组成。

图1 系统组成框图

(1)基带信号发生器:该部分用于根据随机码产生算法产生两路同源的150 MHz 的随机码序列、150 MHz 时钟和相关的开关时钟;需要说明的是为保证信号处理子系统进行脉压后有较好的信噪比,产生的随机码需要具有陡峭的边沿动态特性[1]。该部分电路的设计完全属于高速电路设计,需要考虑信号的完整性问题。

(2)射频调制模块:用于将150 MHz 的宽带随机码字调制到2.4 GHz/900 MHz 的正弦载波上,以适应无线信道的传输,同时可以将天线的尺寸控制在一定范围内;该部分应该还包括一些信号的变换和匹配电路。

(3)射频解调模块:将调制时的同频同相本振载波LO 与接收的射频RF 信号相乘进行相干解调解调出150 M 的数字随机码,并进行适当的整形和放大处理以适应后续电路(采样和信号处理电路)的处理要求,进而得到雷达所需要的距离(基于相关原理)和速度信息(基于多普勒频移)[2-3]。

2 宽带调制解调器设计

为了适合无线信道传输和减少天线尺寸,需要将随机码调制到射频载波上,接收时再进行相应的解调。同时考虑到后续信号处理子系统在脉冲压缩时能有足够的信噪比,此处的调制解调器必须考虑150M 带宽的高速基带信号所必须具有的调制解调带宽,此处的载波选择为2.4 G/900 M。选用的调制解调芯片分别是ADI 公司的ADL5375 和ADL5382[4]。

2.1 宽带调制器设计

(1)宽带BPSK 调制原理及频谱

①BPSK 调制原理

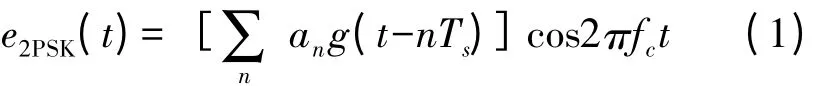

BPSK 的时域表达式通常可以表为:

该式中的an为随机码,g(t)为单个随机码对应的基带脉冲波形,cos2πfct 为正弦载波。在本文中更具体的参数含义如下:an=+1 概率为P;an=-1 概率为1-P。即信码取双极性信号,g(t)取矩形脉冲。

②BPSK 频谱

通过式(1)不难看出,BPSK 调制和2ASK 调制非常类似,可以认为两路2ASK 的合成,所以其频谱分析方法及结论和2ASK 非常雷同。只是两路不同在于an的取值,故可用求2ASK 功率谱密度方法求出[5]。

由该式看出,BPSK 的频谱事实上是将脉冲的频谱搬移至载频处。由于脉冲g(t)频谱为其有效带宽约为1/Ts。因此必须考虑带宽150 MHz随机码基带信号下载频的选择和调制解调芯片的带宽,否则势必会影响调制解调的结果。此处随机码的有效带宽为150 MHz,载频选择2.4 G(fc/(1/Ts)=2.4 G/150 M=16)。

(2)LVDS 标准与调制芯片接口

为适应高分辨率测距的需要,150 MHz 的随机码序列由FPGA 芯片产生并采用差分低电压标准输出(也只有采用该标准才能保证低功耗和信号传输的完整性)。差分低压LVDS 标准具有一定的电特性:1.25 V 左右的直流偏置和约700 mV 的差分摆幅(每个管脚上350 mV)[6-7],而正交调制器ADL5375 要想获得优越的调制性能,要求在输入的基带信号上外加500 mV 的直流偏置(ADL5375-05)[8]。因此,需要将码发生器送过来的差分信号经过电平变换电路将之变为适合调制器工作的电平形式。这就需要设计LVDS 与射频RF 调制器之间的接口。

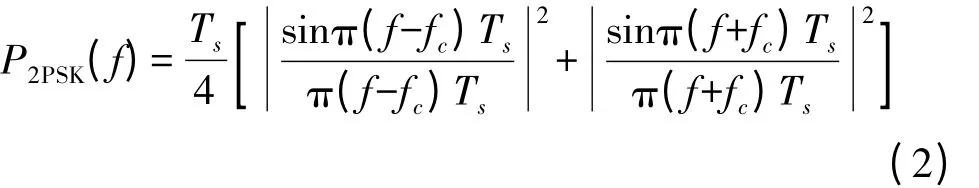

这样的转换电路有2 种设计思路,一是利用有源电路实现,这样可以在不牺牲交流增益的前提下实现直流偏置的变化,但电路较为复杂;二是利用无源的电阻网络实现直流偏置的移动。考虑到后级有放大电路,在此采用方案2。具体电路如图2 中上下两路对称部分电路所示。

图2 调制器电路图

该电路上下两路完全对称部分分别形成两路基带信号的直流偏置。在这里取其中上边一路分析:由于基带信号发生板送来的LVDS 信号具有1.25 V的直流偏置,而送去ADL5375 的信号应为500 mV直流偏置,因此信号的偏置由LVDS2.5 的独立电源提供,采用R2、R4和R6组成无源分压网络,R4和R6连接点处的信号即具有ADL5375 所需要的500 mV直流偏置。但需要说明的是该电路会牺牲一定的交流增益。

(3)调制电路

如图2 所示的调制器电路原理图中ADL5375相关连接是调制器设计的核心部分:该芯片的连接主要包括电源、基带输入、本地载波、射频输出、使能等引脚的连接[7]。

电源和地:VPS1 和VPS2 连接5 V 电源,COM脚(10 个)通过低阻路径连接到相同的地层。每个电源引脚都应就近连上100 pF 和0.1 μF 电容退耦到地。在芯片封装下露出的焊盘应该通过低阻连接到地层。

基带输入:基带输入应该用差分形式驱动,ADL5375 的标准的驱动电压是差分700 mV p-p(350 mV p-p 每个引脚)。而且ADL5375-05 所有基带输入都必须有500 mV 直流偏置。

LO 输入:本振输入设计成为单端源驱动。本地振荡器信号通过串联电容以交流耦合的形式加到LO 引脚同相端(LOIP),此时反相端(LOIN)通过电容交流耦合到地。ADL5375 本振信号的典型驱动电压为0 dBm。

RF 输出端:射频输出在RFOUT 引脚(Pin16)上,可以驱动50 Ω 负载。在大多数情况下,RFOUT脚必须交流耦合到负载。

输出使能端:ADL5375 具有输出无效引脚功能,它通过关断输出放大器以隔离调制器和负载。当DSOP 引脚电压超过2 V 时输出无效。当该脚接地或者悬空时,输出有效。利用DSOP 可以减少LO 射频泄露和降低芯片的宽带噪声到KT 噪声值。也可以将ADL5375 的供电电流从200 mA 减少到131 mA。从DSOP 引脚由高变低(输出由无效到有效)到输出重建需要大约200 ns,从DSOP 引脚由低到高(输出由有效到无效)到输出关断需要在100 ns 左右。

2.2 宽带解调器设计

(1)解调器硬件设计

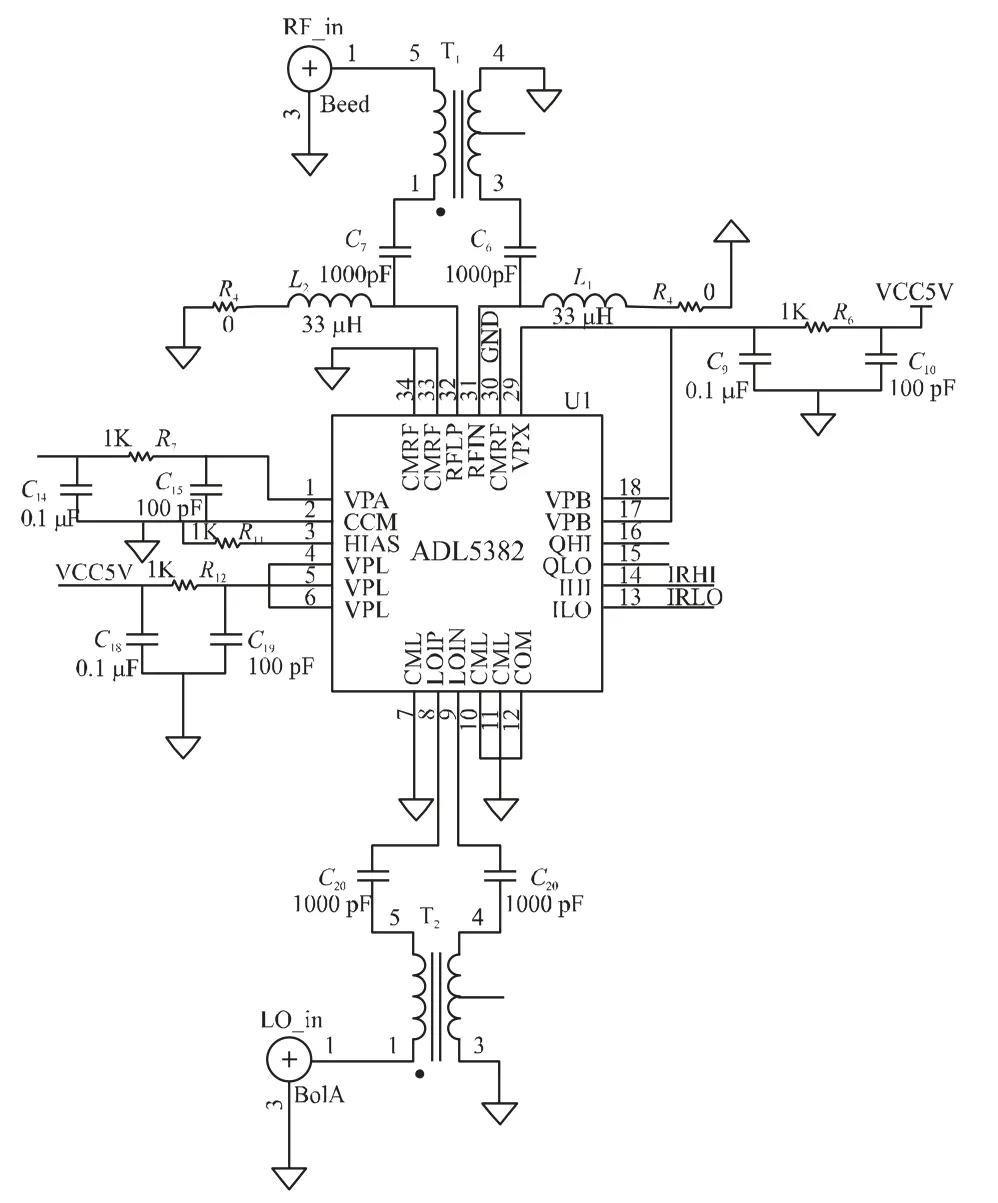

图3 为ADL5382 解调器原理图。在该图中,LO 本振单端输入的信号通过非平衡变压器转换成平衡的差分输入之后,经过电容交流耦合到解调芯片的LOIP 和LOIN 两个差分本振输入端。射频RF 的输入模式和LO 的输入非常类似,至少在进入解调芯片射频输入端RFIP 和RFIN 差分输入端之前通过33 nF 的扼流电感下地。其余输入端多为电源供电,在每个电源管脚附近都并联了大小不一的两个退藕电容[9]。

图3 解调器原理图

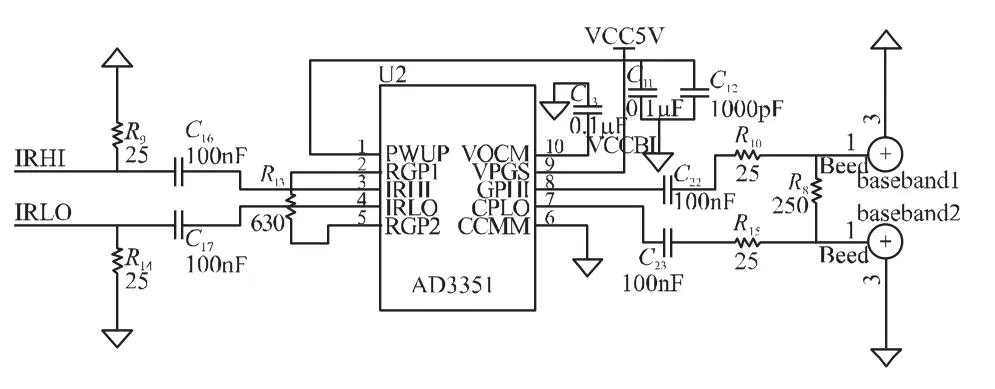

(2)视频放大器及与信号处理系统ADC 的接口设计

ADL5382 解调器的输出不满足LVDS 的电特性标准,需要进行幅度调整和直流偏置变换,同时也为了方便和后级ADC 接口,所以需要加入放大器。由于解调输出是150M 的高速基带解调信号,故需要采用高性能的宽带放大器AD8351。图4 给出了视频放大器的原理图[10]。

图4 视频放大器原理图

2.3 射频PCB 板设计

本系统的基带信号带宽为150 MHz,射频载波RF中心频率2.4 GHz/900 MHz,因此电路设计属于射频电路的范畴,射频电路的设计方法与普通的中低频和数字电路在制作PCB 的时候有很大的区别。一些在低频数字电路中对电路影响不大的因素在射频电路中则可能直接导致设计的成败,特别是信号节点的阻抗匹配问题。因为阻抗不匹配会引起反射和极大的衰耗[11]。

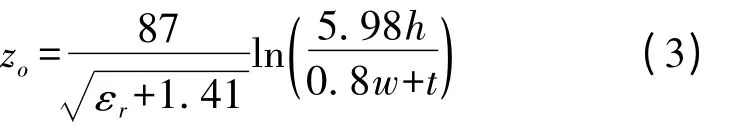

在射频电路中,信号线需要按照传输线的理论分析和设计,必须保证信号线的特性阻抗和信号源及负载的阻抗匹配,这些特性阻抗通常为50 Ω。因此在设计PCB 的时候需要对板材的介电常数、板厚、信号线宽度进行严格的计算,确保信号线的特性阻抗正确。通常,可以用如下公式计算[12]:

其中,zo表示为信号线的特性阻抗,εr表示为板材介电常数,h 表示为板材厚度,w 表示PCB 线宽,t 为PCB 导线厚度。

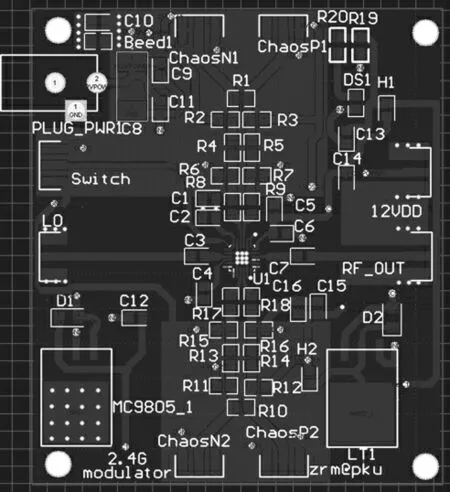

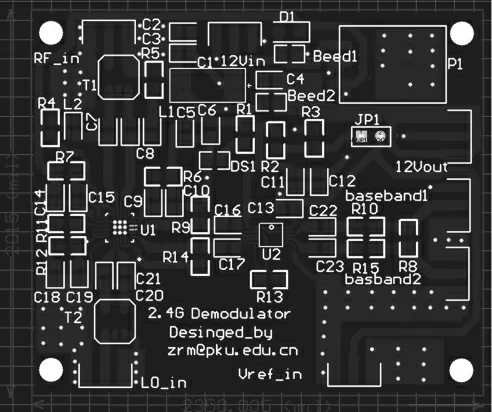

出于对PCB 制作成本的考虑,生产厂家会大批采购某一种介电常数的板材,采用这样的板材设计PCB 时会节约一定的成本。经过和厂家的交流,我们得知厂家最常用的高频PCB 板材介电常数εr为2.55,导线厚度t 为35 μm。根据公式,当特性阻抗一定时,导线的宽度随着板厚增加而变宽,为了布线方便,这里采用最小板厚h 为0.5 mm。根据公式计算,可得到线宽w 为48 mil。图5 和图6 分别给出了调制器和解调器的PCB 图。

图5 调制器PCB 图

图6 解调器PCB

3 系统测试

3.1 测试方案及测试设备

根据项目的设计指标和系统的信号流程,本地载波信号由安捷伦射频信号源N9310A 提供,该信号源频率范围可以从3 kHz 到3 GHz 可调,射频输出幅度/功率也是可调的;输出的波形采用泰克公司的MSO4104 示波器进行测量,其3 dB 带宽为1 GHz,采样率为5 G,探头采用有源探头TAP1500,其带宽为1.5 GHz。

该测试环境中,由码发生器产生150 MHz 的随机码送给调制器,和射频信号源送来经二功分器的射频2.4 GHz/900 MHz 本振进行BPSK 的调制;已调信号和二功分器的另一路本振2.4 GHz/900 MHz信号进入解调器进行BPSK 的解调。中间的各点信号均可以用示波器进行测量。

3.2 测试结果

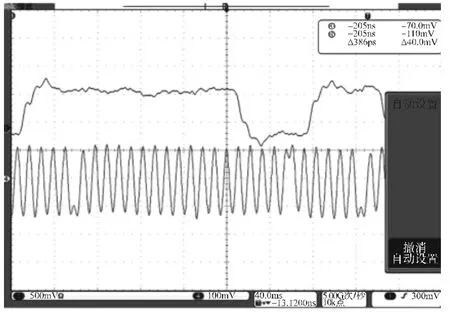

图7 给出了基带信号与已调信号的对应关系,该图表明:①在基带信号跳变时已调信号相位发生翻转,完全符合BPSK 调制原理;②是已调波形与基带信号有一定的延时;③每个码片宽度内刚好对应的是6 个载波宽度,符合基带信号和射频信号的频率比。

图7 基带码发生器输出VS 调制器输出

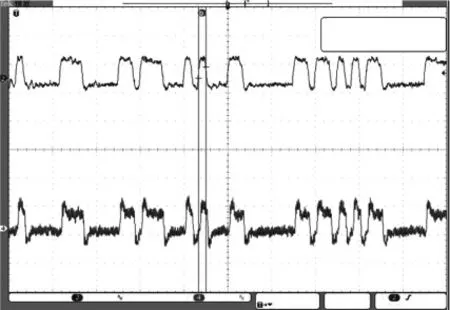

图8 基带码发生器输出VS 解调器输出1

图8给出了基带码发生器输出和解调器输出的对应关系,即收发码元的对应关系。可以看到:一是接收码和发送的码对应关系没有出错;二是接收恢复的码不仅幅度变小了很多,而且有一定的畸变(需要说明的是该图中的波形均采用普通探头而非差分有源探头测得)。

图9 与图8 类似,给出了基带码发生器输出和解调器输出的对应关系。但此时采用的是2.4 GHz 载波。显然,此时的解调的效果优于载波为900 MHz。

图9 基带码发生器输出VS 解调器输出2

4 结束语

实验测试结果表明:采用本文以ADI 公司的调制解调芯片ADL ADL5375 和ADL5382 作为核心的调制解调器,可以正确的对150 M 高速随机码进行调制和解调。将该调制解调器用于随机码脉冲编码雷达中可以实现1 m 的测距分辨率和相应的测速功能。同时由于采用的载波是900 M,解调器输出的波形有一定的畸变将会对脉冲压缩的信噪比产生一定的影响,可以通过提高载波频率至2.4 G 得以改善。

[1] Merrill I Skolnik. Radar Handbook[M]. 3rd ed. New York:McGraw-Hill,2008:386-410.

[2] 张世登.面向混沌码雷达引信的单步预测其研究[D]. 北京:北京大学,2008:1

[3] 章新春.面向混沌码雷达引信的Burg 算法应用研究[D]. 北京:北京大学,2008:5.

[4] 孟杲杲,朱晓华. BPSK 宽带调制解调技术研究[D]. 南京:南京理工大学,2009:51-52.

[5] 周炯槃,庞沁华.通信原理[M].3 版.北京:北京邮电大学出版社,2008:188-189.

[6] 雷铭,邹雪城,陈军.高性能CMOS LVDS I/O 接口单元的设计研究[J].华中科技大学学报:自然科学版,2003,31(4):76-78.

[7] Jeff Waters.National Semiconductor’s LVDS Offers High-Speed Interface with FPGA/CPLD.Component Markets,2006.1.

[8] Analog Devices. ADL5375 Device Datasheet[DB/OL]. http://www.analog.com,2007:1-30.

[9] Analog Devices. ADL5382 Device Datasheet[DB/OL]. http://www.analog.com,2008:1-2.

[10] Analog Devices. AD8351 Device Datasheet[DB/OL]. http://www.analog.com,2004:1-16.

[11] 张仁民. 高速混沌码发生器设计及宽带调制解调技术研究[D].北京:北京大学,2011:44-46.

[12] 郭海鹏. 二次谐波雷达的设计与实现[D]. 北京:北京大学,2010:17-18.