IEEE1394总线接口设计

2011-06-11聂浩许敬旺康晓军唐士建

聂浩 许敬旺 康晓军 唐士建

(北京空间机电研究所,北京 100076)

1 引言

IEEE1394是1986年由苹果公司开发的一种高速数据传输总线,于1995年由美国电气和电子工程师协会(IEEE)制定成标准,旨在取代并行总线SCSI。目前它主要发展为IEEE1394-1995、1394a、1394b、1394c等系列的开放式技术标准。IEEE 1394作为高速数据传输总线,已经被广泛应用于数字摄像机、数字照相机、计算机及其外围设备等,在航空航天领域也有了较多应用[1]。

IEEE1394总线具有异步传输和等时传输两种传输模式。等时模式的大容量实时传输特性使得IEEE1394总线广泛应用于图像传输领域[2]。IEEE1394标准中规定的协议比较复杂,实际应用中大多数采用专用的总线接口芯片。常见的IEEE1394总线设计采用的是主控制器加上总线接口芯片及外围逻辑电路[3]。而IEEE1394总线与嵌入式处理器的结合,进一步提高了设备的集成度与便携性。

从硬件发展来看,IEEE1394协议中的物理层和链路层已经由硬件实现了。目前,TI、NEC、SONY等厂家都生产了具备这两个协议层功能的总线接口芯片[4]。链路层芯片有TI的TSB12LV系列,TSB42AB4,TSB42AA9和SONY的CXD 1947Q等;物理层的控制芯片有TI的TSB41ABx系列 ,TSB41LV0x系列和SONY的CXD1944R等。另外还有物理层和链路层的整合芯片,如TI的TSB43AB2x系列,TSB43AA82等。

DSP(数字信号处理器)作为一种功能强大的微处理器,主要应用在数据、语音、视像信号的高速数学运算和实时处理方面;FPGA(现场可编程门阵列)可以构建高度并行的架构,具有很高的吞吐量和原始数据处理能力。因此,以DSP作为主控制器,FPGA作为协处理器搭建外围逻辑电路的IEEE1394总线接口设计方案,具有较强的现实意义。

2 设计方案

IEEE 1394协议定义了3个协议层:事务层、链路层、物理层;用于在请求者和响应者之间的数据传输过程中完成相关服务。另外还定义了总线管理层,负责总线配置和每个总线节点的活动管理[5]。

事务层是针对异步传输定义的,建立在链路层的异步子事务之上。事务层定义了一整套请求—响应协议来操作读、写、锁定等异步事务,并负责为每个收到的数据包提供确认。链路层是事务层和物理层的接口,将事务层请求和响应转化为相应的数据包发送到串行总线上。物理层负责数据位的发送和接收;仲裁;提供电气和机械接口[6]。

本文介绍了基于链路层芯片TSB12LV32和物理层芯片TSB41AB3的接口设计方案。以DSP为主控制器,FPGA作为外围逻辑电路,共同实现IEEE1394事务层协议,链路层和物理层芯片则作为外设实现数据读取和写入。整体结构框图如图1。

图1 整体结构框图

DSP采用TMS320F240,是TI公司专门为控制应用而优化的16位定点单片控制器。FPGA选用XILINX公司的XC2V1000,具有100万门阵列资源,可以满足本设计需求。

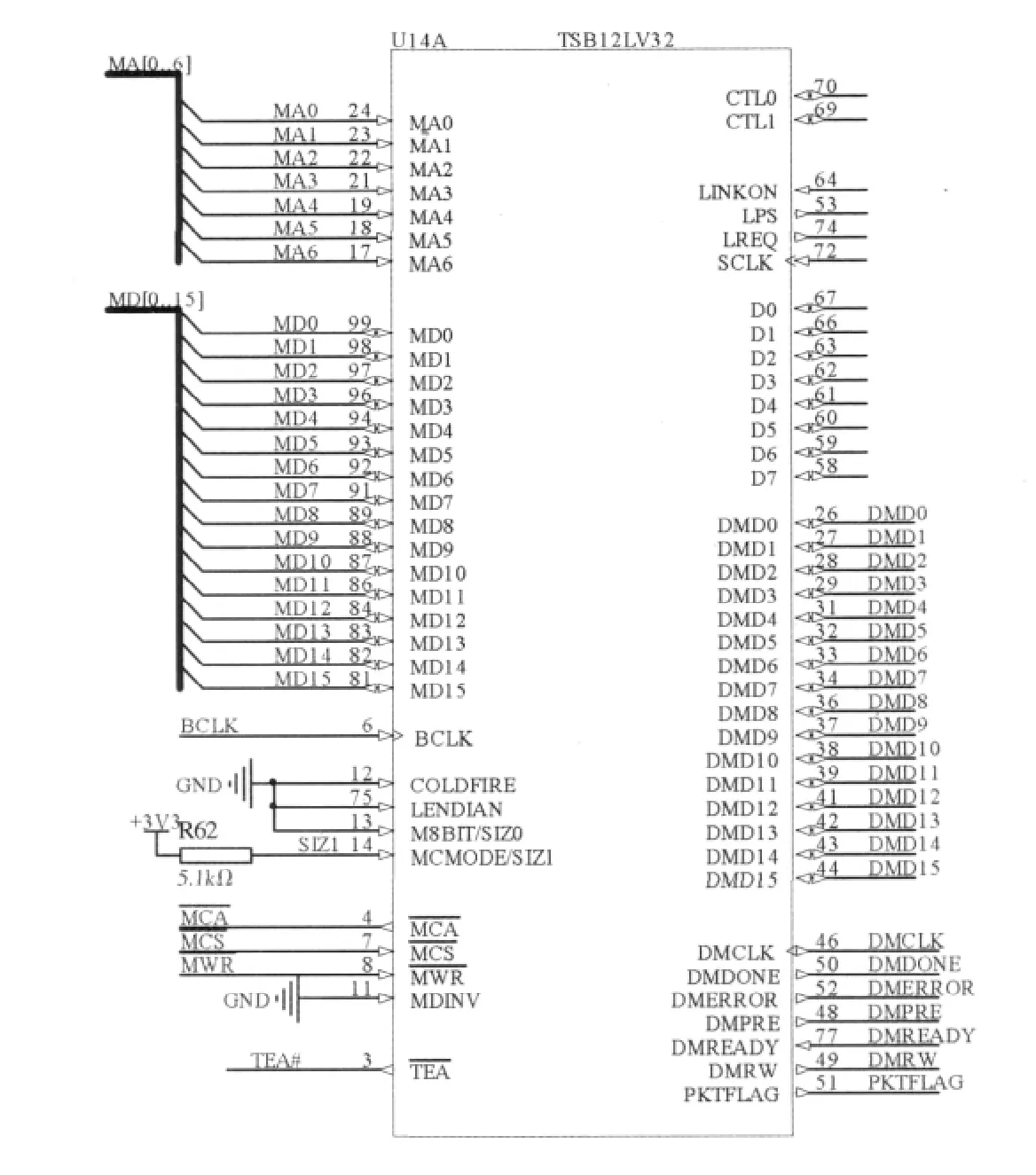

TSB12LV32是一款兼容IEEE1394-1995和1394a的高性能的通用链路层(LLC)芯片,具有微控制器接口和DM(数据迁移)接口两部分端口资源[7],如图2所示。它用于在控制器和IEEE1394物理层芯片以及连接到链路层DM接口的外部设备之间的数据传输,支持400Mbit/s、200 Mbit/s和100 Mbit/s的传输速率。微控制器接口主要用于实现芯片配置和异步数据传输,而DM接口则是用来实现传输量大的等时/异步数据流包的传输。芯片内部采用7位地址线寻址00h至4Ch空间的配置寄存器(CFR),所有链路层内部寄存器CFR空间为32位宽,每8位空间占用一个地址。并分别内置了2kbyte大小的通用接口FIFO(GRF)和异步传输FIFO(ATF),用于链路层微控制器接口和物理层接口之间的数据包传送。

图2 TSB12LV32内部功能模块图

TSB41AB3是一款三端口兼容IEEE1394-1995和1394a标准的物理层(PHY)芯片[8]。TSB41AB3提供3个物理端口,每个端口都有单独的线缆偏置电压和终端驱动器供电电压;支持等时传输和异步传输,支持100 Mbit/s、200 Mbit/s、400 Mbit/s的传输速率,能和链路层芯片实现无缝连接,具有较高的通信速率与稳定性。

3 IEEE1394接口电路设计

依据上述设计方案,IEEE1394接口电路设计包括如下部分:控制核心DSP+FPGA、FPGA与链路层的接口、链路层与物理层的接口、物理层与连接器的接口。

3.1 DSP+FPGA

本设计利用DSP+FPGA架构实现IEEE1394事务层协议,控制链路层芯片和物理层芯片。DSP作为系统核心,包括了整个系统的控制和运算部分。FPGA可以构建高度并行的架构,能承担繁重的计算工作量,能提供更高的吞吐量和原始数据处理能力。结合DSP和FPGA作为软硬件协同设计平台的显著特点是结构灵活、有较强的通用性、适于模块化设计、能提高算法效率、易于维护、系统扩展性强。

DSP最小系统包括时钟电路、看门狗电路、程序存储及数据存储电路[9];FPGA电路包括时钟电路、配置电路和JTAG仿真电路。由于DSP最小系统和FPGA配置电路都已经是相当成熟的电路结构,所以本文不多展开叙述。

FPGA芯片 XC2V1000-4BG575具有100万门阵列资源,328个可配置的通用IO管脚[10],与DSP芯片和IEEE1394链路层芯片的管脚连接具有高度的灵活性。图3是DSP与FPGA之间控制、地址、数据总线的连接框图。

图3 DSP与FPGA连接框图

DSP的软件程序应实现对链路层芯片和物理层芯片的配置、对IEEE1394通信的控制。而DSP的读写时序与链路层芯片的时序要求不相符,故需要FPGA构建时序转换模块,以匹配DSP和链路层芯片的接口时序。

3.2 FPGA-链路层接口

链路层芯片TSB12LV32外部端口包括微控制器接口和DM接口两部分。FPGA的通用IO管脚与之相连接,实现寄存器配置、异步控制、等时传输等功能。

本设计中使用链路层的微控制器接口来进行对其内部寄存器的配置以及异步事务的操作;使用DM接口进行等时事务的操作。这样将异步、等时事务在事务层端的物理接口上独立开来,那么事务层在处理这两类事务时使用独立的控制逻辑,而不用在DSP单线程任务中挤占有限的资源,使得系统架构更清晰,控制逻辑更简化,并且提高了事务层控制效率。图4是FPGA与链路层的微控制器接口和DM接口连接框图。

图4 FPGA与IEEE1394链路层芯片连接框图

(1)微控制器接口

TSB12LV32包含一个可编程微控制器接口,它具有8位/16位可选的数据总线,7位地址总线,5种不同工作模式和高达60MHz的BCLK频率。数据总线以MD0为MSB(最高位),地址总线以MA0为MSB。工作模式包括字节(8位)握手模式、双字节(16位)握手模式、字节(8位)固定定时模式、双字节(16位)固定定时模式、Motorola ColdFire模式。

MCS(微接口周期启动)是链路层的低电平活动的输入引脚,它表征主控制器开始通过微控制器接口访问链路层。 MCA(微接口周期确认)是一个低电平活动的输出信号,代表从链路层微控制器接口发送到主控制器周期确认信号。 MWR是读/写指示引脚,为高电平时,表示对链路层的读访问操作;为低电平时,表示对链路层的写访问操作。微控制器接口上的所有数据传输均使用BCLK的上升沿进行同步。TEA是传输错误确认引脚。此信号指示数据传输操作中出现的错误。

(2)DM接口

DM(数据迁移)接口是一个8/16位高速接口,支持频率为24.576MHz来自非缓冲端口的等时、异步和异步数据流发送/接收。它是用于处理大型数据包的外部存储器接口。DM口在同一循环周期内可支持4个等时信道进行等时发送。DM端口具有8种工作模式,包括等时接收/传送,异步接收/传送;每种又有自动包头加载和非自动包头加载两种模式。DM接口具有7个控制引脚。这些引脚的功能的详细信息和相关控制时序,可参阅TSB12 LV32数据手册。

图5是FPGA与链路层的微控制器接口和DM接口的连接原理图。

图5 链路层芯片微控制器接口与DM接口原理图

(3)状态引脚

图6是FPGA与链路层状态引脚的连接原理图。

在硬件复位期间将对TSB12LV32的DIRECT引脚采样以确定是否存在电隔离。如果该引脚为高电平,则不存在隔离。如果该引脚为低电平,则使用了TI总线支架隔离。

链路层上的CONTNDR引脚在硬件复位时默认为输入。在图6中,CONTNDR经过一个1kΩ电阻接地。表征该节点并非用于等时资源管理器(IRM)或总线管理器功能。但在加电之后,可以用链路层控制器内的CTNDRSTAT位从内部驱动此引脚的值。

在本设计中,M8BIT/SIZ0引脚接地,MCMODE/SIZ1引脚上拉,可将LLC设置为以双字节(16位)握手模式与主控制器进行通讯。该器件未配置为Motorola ColdFire模式,ColdFire引脚也接地。

LENDIAN引脚若为高电平,微接口被设置为little-endian模式,那么在将数据写入器件的内部FIFO或配置寄存器(CFR)之前,MD0-MD15的数据会以字节方式交换。本设计LENDIAN被接地。可以使用MDINV和MCMODE/SIZ0引脚将微接口配置为数据不变或地址不变模式。但是,仅当启用了LENDIAN(高电平),MDINV才有意义。

STAT0~STAT2是常规状态输出引脚。这些引脚可以独立编程以显示14个可能的内部硬件状态中的一个状态。有关STAT0~STAT2编程的详细信息,参阅TSB12LV32数据手册(TI文献编号SLLS336B)。

CYCLEIN输入引脚是可选的外部8kHz时钟,用于设置等时周期时钟。本设计中未使用外部输入等时时钟。INT是低电平活动的输出终端,代表所有内部中断的逻辑或非。

图6 链路层芯片状态引脚连接原理图

3.3 链路层-物理层接口

LLC芯片TSB12LV32需与TI公司的PHY芯片配套使用。图7显示了TSB12LV32与TSB41AB3连接的LLC-PHY 接口。 LLC-PHY 接口由 SCLK、CTL0-CTL1、D0-D7、LREQ、LPS、LINKON(C/LKON)和 DIRECT(ISO)引脚组成。

图7 LLC-PHY连接框图

SCLK是由PHY提供的49.152MHz的接口时钟。LLC-PHY接口上所有的控制和数据信号使用SCLK上升沿进行同步和采样。

在本设计中未实施LLC与PHY的隔离,DIRECT和ISO均上拉,PHY和LLC使用同一接地面。要降低电磁干扰发射并降低SCLK线路上的反射,建议使用串联阻尼电阻,应将此电阻放在尽量靠近PHY的位置。通过降低SCLK的边缘速率,串联电阻可以显著降低当PHY与链路层之间的距离较大时可能出现的反射。

CTL0-CTL1引脚是一个双向控制总线,它控制PHY和LLC之间信息和数据的流向。这两个引脚一般由PHY驱动。CTL编码遵循IEEE1394a规范。

D0-D7引脚是双向数据总线,它被用于在PHY和LLC之间传送状态信息、控制信息、或包数据。器件支持S100、S200、S400的数据传输速度。在S100速度下,仅使用D0和D1;在S200速度下,使用D0-D3;在S400速度下,使用D0-D7全部。

LERQ引脚表示由TSB12LV32给出到PHY的链路层请求信号。LREQ用于指示访问总线进行数据包传输的请求,或对PHY寄存器空间的访问请求,或控制仲裁加速。

LPS引脚表示LLC电源状态。LPS被LLC驱动输出给PHY,它表明LLC已经上电并活动,LPS的默认频率是1/16的BCLK频率,也可以被设置为其他值,为防止干扰,将LPS下拉。

PHY的C/LKON发出一个唤醒通知给LLC的LINKON引脚,并在LLC不活动时给它一个中断。当LLC检测到这个引脚活动时,会驱动LPS输出。C/LKON活动时是一个4M-8MHz的时钟信号,存在时间不超过500ns。

在TSB12LV32给出总线请求时,TSB41AB3会在获得总线控制权后进行初始化传输操作;在TSB41AB3授权TSB12LV32控制LLC-PHY接口之后,传输操作初始化完成。图8是链路层与物理层接口的连接原理图。

CPS引脚检测线缆是否提供电源并经过400kΩ电阻连接到线缆电源。若线缆提供电源,该节点应始终使CPS引脚经过400kΩ电阻连接到线缆电源。如果没有线缆电源,则可以将CPS直接连接到PHY地。

XI,XO是晶振输入端口,须连接到24.576MHz的基准时钟输入。这个时钟驱动内部锁相环(PLL)产生所需的各种时钟,用作传输控制和实现器件之间的同步。

RESET引脚拉低将复位内部逻辑。此引脚提供了内部上拉至VDD。

R0和R1引脚设置内部工作电流和电缆驱动器的输出电流。要满足IEEE 1394-1995标准输出电压限制,需要使用6.34(1±1%)kΩ的电阻。

TESTM、SE和SM引脚是用于制造测试过程中的控制引脚。对于正常操作,TESTM必须经过一个1kΩ电阻连接到DVDD(3.3V)。SE和SM须接地。

PC0-PC2是电源类型可编程输入端口,用来设置自标识包中的电压类型的默认值。“100”表示节点可以从总线上获取3W的电源输入,也可以提供电源到总线。

如果未执行PD的断电选项控制,则应将PHY上的PD引脚经过一个1kΩ电阻接地以保持PHY被启用。

须将电源引脚(DVDD、AVDD、和PLLVDD)单独分组,然后经过几个高频去耦电容将它们去耦接GND引脚。

3.4 物理层-连接器接口

TSB41AB3有3个电缆连接端口。接口包括线缆、线缆地线、双绞线TPA+/TPA-、双绞线TPB+/TPB-。双绞线TPA上传送差分选通信号,并接收差分数据。双绞线TPB上传送差分数据,并接收差分选通信号。本设计中使用2个电缆连接端口,且不使用线缆电源VP和线缆地线VG。图9是物理层芯片的两对双绞线连接示意图。

图9 PHY与连接器接口示意图

每个端口 (TPA和TPB)的驱动器设计为与外部112Ω端接电阻网络一起工作。传输线上差模信号以100MHz/200MHz/400MHz的频率产生,用于复位和仲裁,总线配置以及数据包传输。IEEE1394差模信号在传输线上的特性阻抗为(110±6)Ω,使用112Ω(选用2个56Ω标称电阻串联)的终端电阻器来消除每个信号线上的反射[4]。TPA电阻网络的中点直接连接到TPBIAS,考虑稳定性连接了一个1μF电容,为降低TPBIAS上的电磁干扰可连接一个270pF电容。TPB电阻网络的中点经过并联的RC网络耦合接地。应将这些112Ω端接电阻网络安装在尽量靠近PHY的位置,否则会吸引多的噪声信号。

图10是物理层与连接器之间的连接原理图。

图10 PHY-连接器接口原理图

当不使用PHY的某个连接端口时,必须正确端接它。首选方法是在IEEE1394a模式下配置端口。在IEEE1394a模式下,可以经过1μF电容将TPBIAS接地或保持悬空;TPB+和TPB-引脚须连接在一起并接地,TPA+和TPA-引脚可以保持悬空。

4 结束语

本文介绍了利用DSP+FPGA与接口芯片实现IEEE1394总线通信的总线接口电路设计。该设计具有一定的通用性,在实际测试中,可以实现对总线接口芯片寄存器的正确配置和读取操作;IEEE1394总线接口电路与总线测试设备连接正常,数据通讯正确。本设计的接口方案对采用其他主控制器实现IEEE1394总线通信的电路有借鉴参考作用。

[1]张大朴,王晓,张大为.IEEE1394协议及接口设计[M].西安:西安电子科技大学出版社,2004:5-6.

[2]龚东磊.胡继波.IEEE1394高速串行总线及其应用[J].计算机工程,2002,28(11):237-239.

[3]陈志文.IEEE 1394接口及其应用[J].世界电子元器件,2001(12):11-12.

[4]李世平,戴凡,汪旭东.IEEE-1394(Fire Wire)系统原理与应用技术[M].西安:西安电子科技大学出版社,2004:172-181,16-20.

[5]Don Anderson.Fire Wire(R)系统体系.第二版1394a[M].姜汉龙译.北京:中国电力出版社,2001:42-46.

[6]马金发.IEEE1394的体系结构[J].现代计算机,2002(1):9-12.

[7]TSB12LV32/TSB12LV32I:IEEE1394-1995 and P1394a Compliant General Purpose Link Layer Controller[R].SLLS336B,US:Texas Instruments,April,2000.

[8]TSB41AB3 IEEE 1394a-2000 THREE-PORT CABLE TRANSCEIVER/ARBITER[R].SGLS122B,US:Texas Instruments,2004.

[9]崔艳召,汤恩生,许敬旺.TMS320LF2407系统设计及外扩CAN总线设计[J].航天返回与遥感,2008,29(2):48-52.

[10]VirtexII Platform FPGAs:Complete Data Sheet[R].DS031_V3.4,US:Xilinx Inc.,2005.