基于FPGA的接口芯片逻辑设计及仿真

2011-02-03王文涛张皓月朱顺安

王文涛,张皓月,朱顺安,周 佳

(中南民族大学计算机科学学院,武汉430074)

随着微型计算机应用的日益广泛和深入,接口技术有了迅速的发展,并已成为直接影响微机系统功能和推广应用的关键.从硬件的角度来看,微机的开发与应用,在很大程度上就是微机接口电路的开发与应用.FPGA是一种新兴的可编程逻辑器件,可以取代现有的全部微机接口芯片,实现微机系统中的存储器、地址译码等多种功能,具有更高的密度、更快的工作速度、更好的稳定性和更大的编程灵活性,能熟练运用FPGA设计接口芯片,无疑需要对接口芯片有更深层次的理解.

1 8255A内部结构

8255A具有24个可编程设置的I/O口,即3组8位的I/O为 PA,PB和 PC[1].它们又可分为2组12位的I/O,A组包括A口及C口(高4位,PC4~PC7),B组包括B口及C口(低4位,PC0~PC3).A组可设置为基本的I/O口,闪控(STROBE)的I/O闪控式,双向I/O 3种模式;B组只能设置为基本I/O或闪控式I/O 2种模式,而这些操作模式完全由控制寄存器的控制字决定.

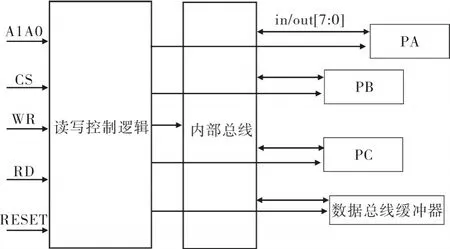

如图1,我们将8255A划分成6个模块,分别是数据总线缓冲器、读写控制逻辑、内部总线、PA、PB、PC[2].

图1 8255A内部结构图Fig.1 Internal structure of 8255A

各信号的说明如下.

A1A0:可以形成片内4个端口地址,用来寻址8255A内部寄存器.

CS:芯片选择信号线,当CS=1时,表示芯片被选中,允许8255A与 CPU进行通讯;CS=0时,8255A无法与CPU做数据传输.

WR:写信号,当WR=1且CS=1时,允许CPU将数据或控制字写入8255A.

RD:读信号,当RD=1且CS=1时,允许8255A通过数据总线向CPU发送数据或状态信息,即CPU从8255A读取数据.

RESET:复位输入线,当该输入端处于高电平时,所有内部寄存器(包括控制寄存器)均被清除,所有I/O口均被置成输入方式.

2 各模块功能描述和实现

2.1 数据总线缓冲器

数据总线缓冲器负责在CPU与内部总线建立数据传输通道.CTRL[4]、CTRL[3]、CTRL[1]和CTRL[0]分别表示PA和PC高四位、PB和PC低四位的传输方向;CTRL[]=0表示输出,CTRL[]=1表示输入[3].

2.2 内部总线

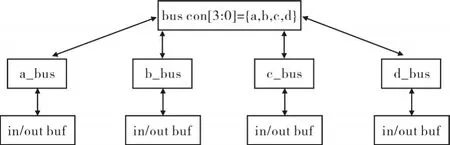

内部结构如图2所示,内部总线在数据总线缓冲器和A口或B口或C口之间建立数据传输通道.

图2 8255A内部总线结构图Fig.2 Internal bus structure of8255A

bus_con[3∶0]中只能有一位为1,其余均为0;为1的那位就输出数据到bus[7∶0]中.其他均处于从bus[7∶0]读数据状态.

2.3 读写控制逻辑

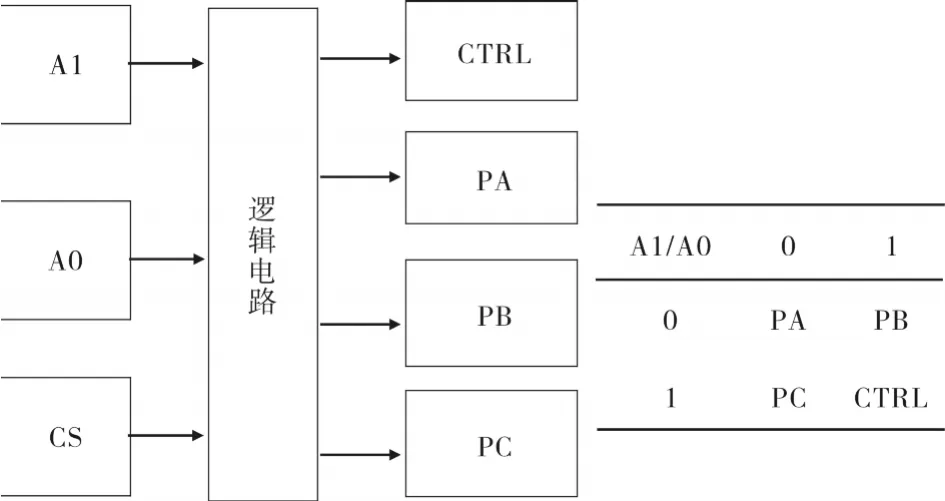

读写控制逻辑根据输入信号的控制,输出对整个8255A的控制信号.根据输入信号的功能可以此模块分成以下几个部分.

1)A、CS组成的控制信号.

2)WR、RD组成的读写信号.

WR=1,RD=0 时,表示读数据;WR=0,RD=1时,表示写数据.

图3 A和CS的控制信号Fig.3 Control signal of A and CS

3)对数据总线缓冲器的控制信号[4].

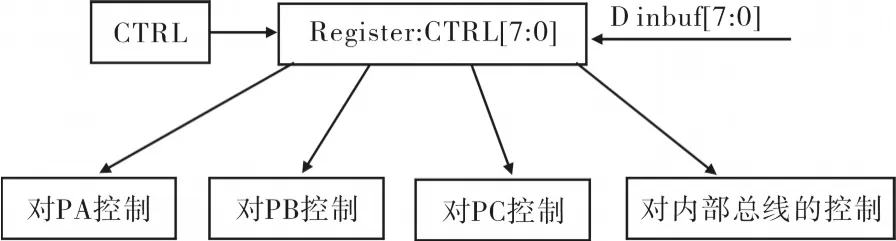

当 RESET=1 时,CTRL=8’b0;当{A,CS,D[7],reset,WR}==6’b110100 时,表示对读写控制逻辑的寄存器进行操作.即CTRL=D_inbuf;根据CTRL[]寄存的数据来产生对其他口的控制逻辑.

图4 CTRL的控制逻辑Fig.4 Control logic of CTRL

4)对PA的控制.

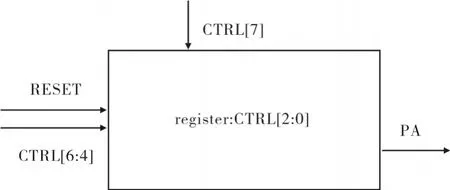

如图5所示,当 RESET=0,CTRL[7]=1时,PA输入或输出由 CTRL[4]控制,PA的方式由CTRL[6∶5]控制.

图5 对PA的控制Fig.5 Control logic for PA

5)对PB的控制.

与PA类似,只是 CTRL[6∶4],PA分别换成CTRL[2∶1],PB;并且 CTRL[4]换成 CTRL[1].

6)对PC的控制.

当 RESET=0,CTRL[7]=1 时,CTRL[3]和CTRL[0]分别控制 PC[7∶4]和 PC[3∶0]的输入或输出,即CTRL[]=0表示输出,CTRL[]=1表示输入.

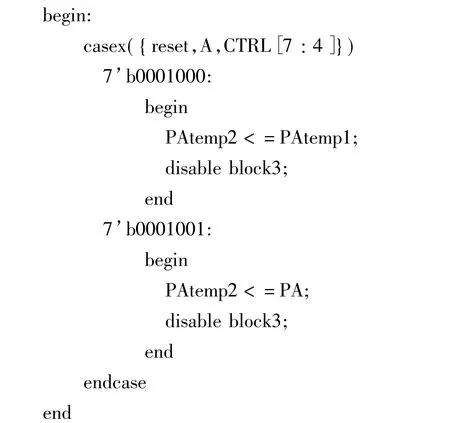

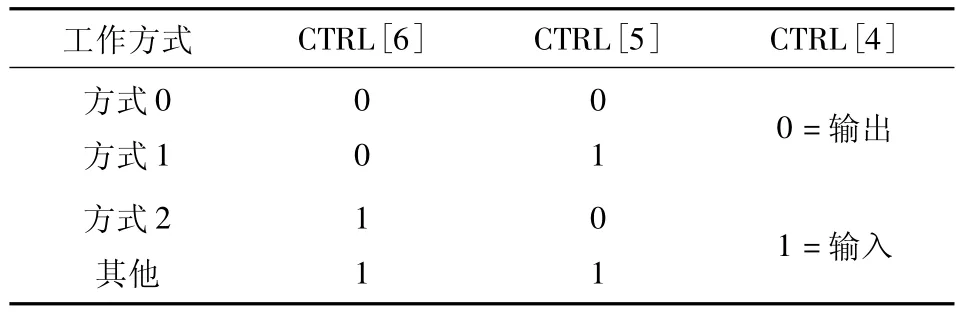

2.4 A 口

如表1所示,A组有3种方式(0方式、1方式、2方式),由 CTRL[6∶5]控制,传输方向由 CTRL[4]控制.关于 PA 的部分代码[3]如下:always@(PAtemp1,PA,reset,A,CTRL)

表1 PA的命令字Tab.1 Command word of PA

2.5 B 口

依2.3所述与A口类似,故不赘述.

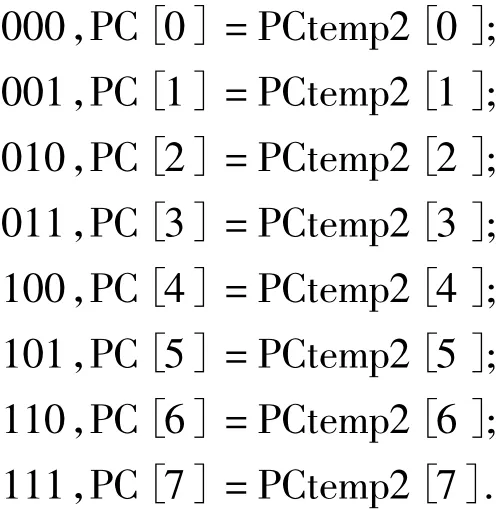

2.6 C 口

C口作用与8255A的工作方式有关,除了作数据口以外,还有其他用途.

i)作状态口.8255A在1、2方式下有固定的状态字是从C口读入.

ii)作按位控制用.C口的8个引脚可以单独从1个引脚输出高/低电平.

以下是对内部寄存器:PCtemp1[7∶0],PCtemp2[7∶0]的分析.

(1) 对于 PC[3∶0]的处理.当 PC[0]=1 时,PC[3∶0]有效,PC[3∶1]的值是:

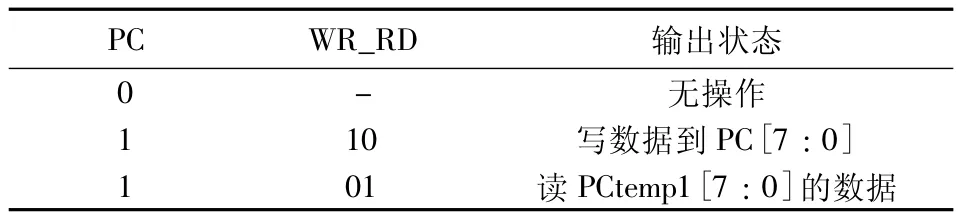

(2)C口读写控制如表2.

表2 C口读写控制Tab.2 Read and write control of PC

(3)C口高/低4位输入/输出方式如表3.

表3 C口的输入/输出方式Tab.3 Input/output of PC

3 仿真与分析

设计完成后,进行各项功能测试,以测试性能是否满足技术要求.

图6为测试平台硬件实物,采用Xilinx公司的Spartan-3E 系列 FPGA[5,6],3.3V 电源供电,在此平台上完成对8255A代码的测试.

图6 测试平台硬件实物Fig.6 Hardware test platform

我们进行的是8255A方式0的仿真.在0方式下,彼此独立的两个8位和两个4位并行口,共24根I/O全部由用户支配,都能被指定作为输入或者输出用.需要注意的是,C口的高4位或低4位只能作为一组同时输出或输入,不能把4位中的一部分作输出,另一部分作输入.

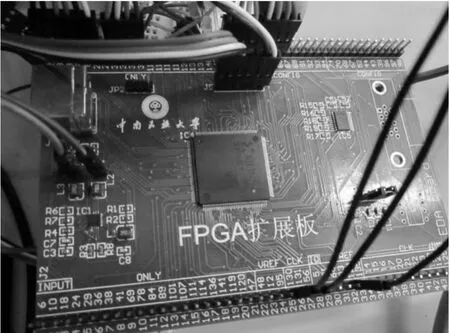

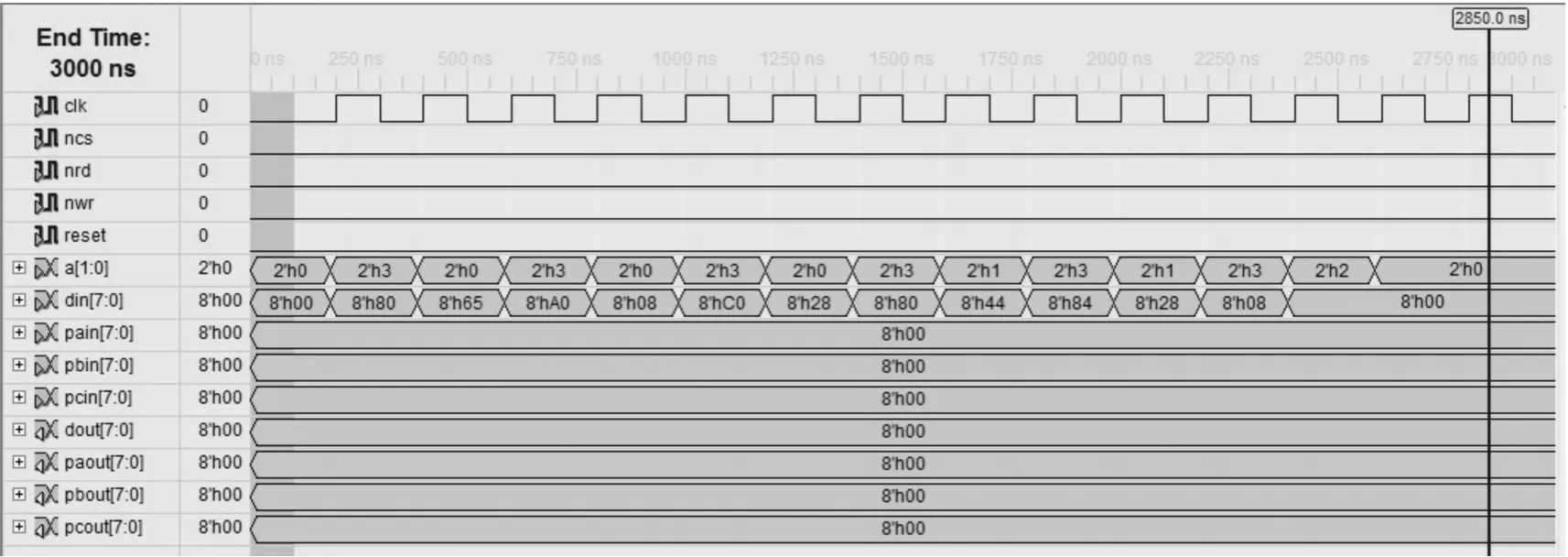

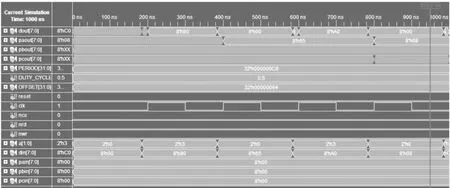

经PACE分配引脚,然后通过 JTAG方式将8255A的代码下载到FPGA上,并给出如图7激励,得出仿真结果如图8.

激励如图7,a[1∶0]在 0 ~180ns为 2’h0,即00,此时选中PA,但无控制字;180~380ns为2h’3,此时选中 din[7∶0]作为状态控制字,din[7∶0]为8’h80,即10000000,此状态控制字表示,A组和 B组为 0方式,PA、PB和 PC为输出状态;380~580ns,a[1∶0]为2’h0,din[7∶0]为8’h65,则选中PA,并且将 din[7∶0]的值送给 paout[7∶0].

仿真结果如图8,a[1∶0]在 180 ~380ns为 2’h3,选择 din[7∶0],此时 din[7∶0]为 8’h80,并将其值送入CTRL.在380 ~580ns,a[1∶0]为2’h0,此时PA被选中,且为输出状态,可以看到din[7∶0]为8’h65,而在 400 ~800ns,paout[7∶0]为 8’h65,说明此时paout输出的值为din[7∶0]里的值,由此实现了8255A的0方式.

图7 测试波形Fig.7 Testbench wave

图8 仿真结果Fig.8 Results of simulation

4 结语

本文在FPGA上实现了8255A芯片的基本功能,亦可根据需要,修改参数,任意扩展位数.下一步的工作是通过修改、完善和测试将其封装成IP核,并且以此作为范例将其他所需的芯片也封装成IP核,方便调用.

[1]刘乐善.微型计算机接口技术及应用[M].武汉:华中科技大学出版社,2000:137-165.

[2]吕志鹏.16位微处理器在FPGA上的设计与原理实现[D].北京:清华大学,2004.

[3]Davide P,Scott T.Practical FPGA programming in C[M].Boston:Prentice Hall PTR,2007:19-51.

[4]刘 岚,黄秋元,陈 适.FPGA应用技术基础教程[M].北京:电子工业出版社,2009:151-177.

[5]王文涛,王 建,朱顺安.基于FPGA的女书文字切割技术的设计与应用[J].中南民族大学学报:自然科学版,2011,30(1):96-100.

[6]孙 航,胡灵博.Xilinx可编程逻辑器件应用与系统设计[M].北京:电子工业出版社,2008:84-102.