基于FPGA的传真译码电路设计与实现

2010-08-06支亚军刘意先

支亚军, 蒋 林, 刘意先

(西安邮电学院电子工程学院,陕西 西安710061)

0 引言

传真通信中,需要把要扫描后的数据进行 A/D转换和二值化处理,转化成表示连续黑白点的1/0数据,再对该数据序列进行编码后发送。接收端对收到的编码数据进行译码,最后输出到打印头。传真数据的编译码,是传真通信关键技术之一。

一维改进的Huffman码(MHC)是在数据压缩中较常使用的一种变长编码。它是ITU-T.4标准中推荐的一维标准编码方法,主要应用于三类传真机[1]。MHC编码表是根据一组典型文件游程概率分布的统计均值构造出来的,它的形成是由形成码和终止码组合实现的,能够用较短的编码来表示较长的连续黑点或白点。这样,编码后一行的数据量大为压缩[2]。

1 传真译码原理分析及译码表构造

对于MHC而言,首先它是一个变长码,发送端在编码时把游程长度所对应的码元数据不留间隙的存入发送缓冲区中,再调制载波后发送出去。接收端解调出来的数据就是编码数据,译码时从数据序列中分离出码字,再根据编码查找码表中所对应的游程长度,输出到打印缓冲区,就完成译码过程[3]。

MHC主要改进的是将码字分为终止码和形成码,0到63的游程长度用终止码表示,64整数倍的游程长度由形成码表示,任意游程长度大于63的码字表示为“形成码+终止码”。例如,当白游程长度为65(64+1)时,编码表示为11011 000111,即白游程长度64的形成码11011加上白游程长度为1的终止码000111。

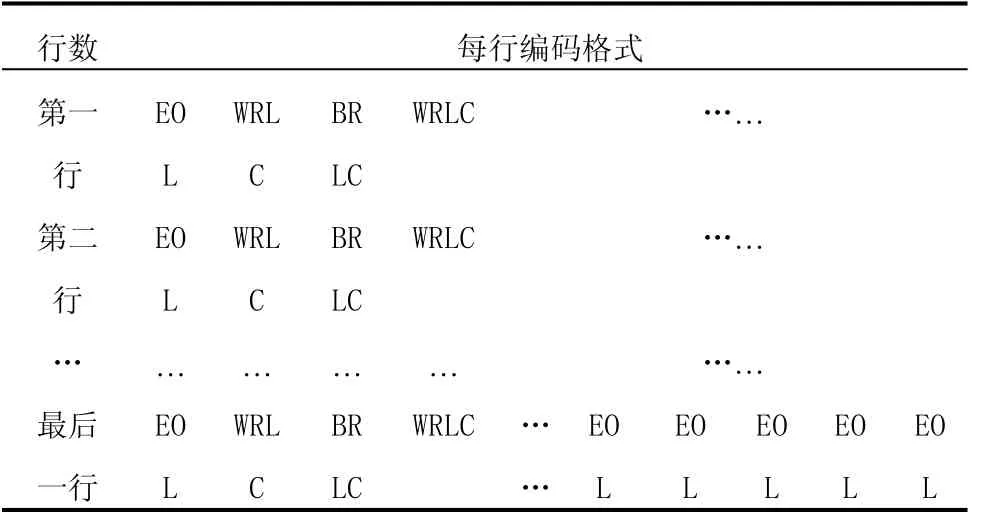

EOL(End of Line)为行结束符,也为行同步标志。每个EOL后面数据为本行的编码,WRLC(White Run Length Coding)为白游程长度编码,BRLC(Black Run Length Coding)为黑游程长度编码,每一行的第一个游程长度编码为白码字,黑白游程长度码字连续交替。收到连续的六个EOL后表示该页结束。根据T.4的表述,一张编码后的传真数据格式如表1所示。

表1 传真编码数据格式

译码的基本思想,构造出译码树,把序列中所包含的所有码字都分配到一个端点上。这样一来,每一个码字与树图编码时类似,以码字首位码元开始,从树根起上移一步,到达一级节点,再以次位码元为依据,再上移到高一级节点上,继续下去可达到端点节点,即叶节点,这样就实现了码字的分离。显然,从树根起每上移一级节点,必须提供节点信息,即该节点是中间节点还是终端节点。为查询方便,树中的每一个节点,分配一个地址,用来存放节点信息。在节点信息上还应提供是形成码节点还是终止码节点。若是形成码节点,地址中存放的二进制数据再乘以 64就是所译出的游程长度;若为终止码,地址中的值就是该码子所对应的游程长度。中间节点地址中存放的二进制数据是下一步搜索地址信息即基址[4]。

显然,要提高译码速度,可以采用多步合一的方法,减少查找码表的次数,也就是一次输入多个码元,根据码表的特点,对白译码而言,第一次可直接输入4个码元,对于黑译码,第一次可输入2个码元,随后每次可输入2个码元或1个码元。

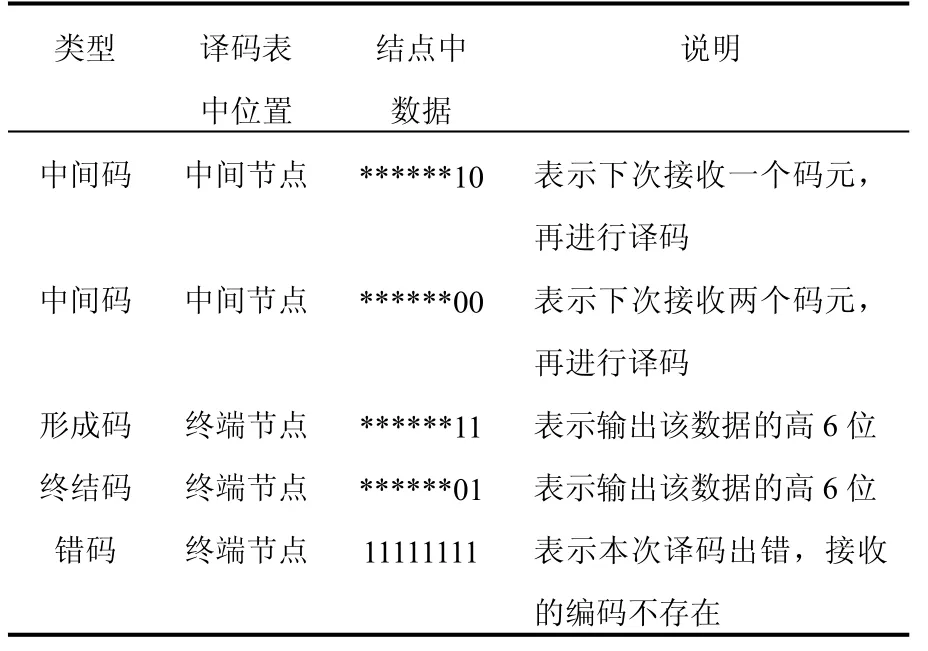

根据MHC的特点和快速译码的思想,并采用地址散列的原理思想,构造出简单有效的译码表,每次译码时产生查表地址时钟周期都是确定,适合于在FPGA上进行传真译码的电路设计。译码表中的节点按类型可分为表2中的5类。

表2 节点类型说明

中间码下次译码时会产生新的子节点,其中第一种根据下步要进的两个码元会有四种可能:00,01,10和 11,所以对子节点分配连续的四个地址,且从地址最低位 10开始分配;第二种根据下步要进的码元有两种可能:0和 1,需要连续的两个地址,并且从地址最低位为 00的地址空间开始分配。这样才符合对节点位置和属性的描述并且满足下步搜索所需要的地址结构。每4个地址空间或2个地址空间都采用地址散列的思想,即对于本次中间节点中的数据其实就是一个未被分配的地址。由于白码表和黑码表中码子个数都一样多,再加上中间节点,可以确定码表的大小。基于以上的分析,对白码表和黑码表都分配256*8的存储单元。

以白译码表为例,第一次译码可先进四位码元,所以最开始会有16种可能的码字0000~1111,它们分别对应地址为00000000~00001111,即将初始码型高位补零形成8位地址。输出对应地址中的数据,如果该数据的最低两位为“10”,表示下次来两个码元后再译码,当下次来的码元00、01、10或11,直接与当前数据相加,即为下次译码地址,通过该地址读出数据。

2 MHC译码电路设计实现

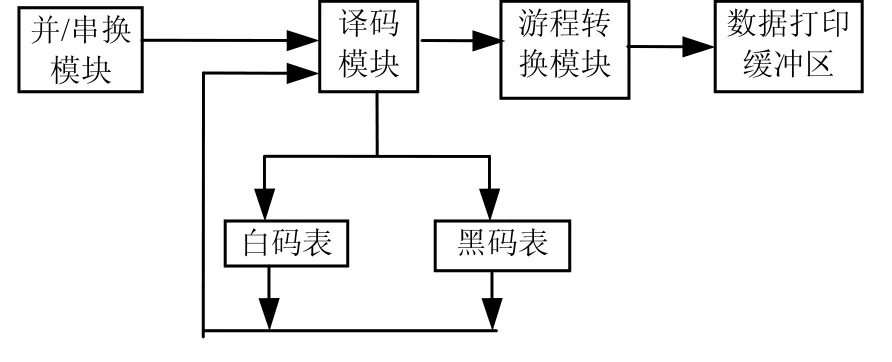

译码时,需先进行并串转换,串行数据再送给译码模块。译出码字后送该数据到游程输出模块,该模块完成代表黑白点的1/0数据的输出,再送往行数据打印缓冲区。系统模块如图1所示。

图1 传真译码电路框

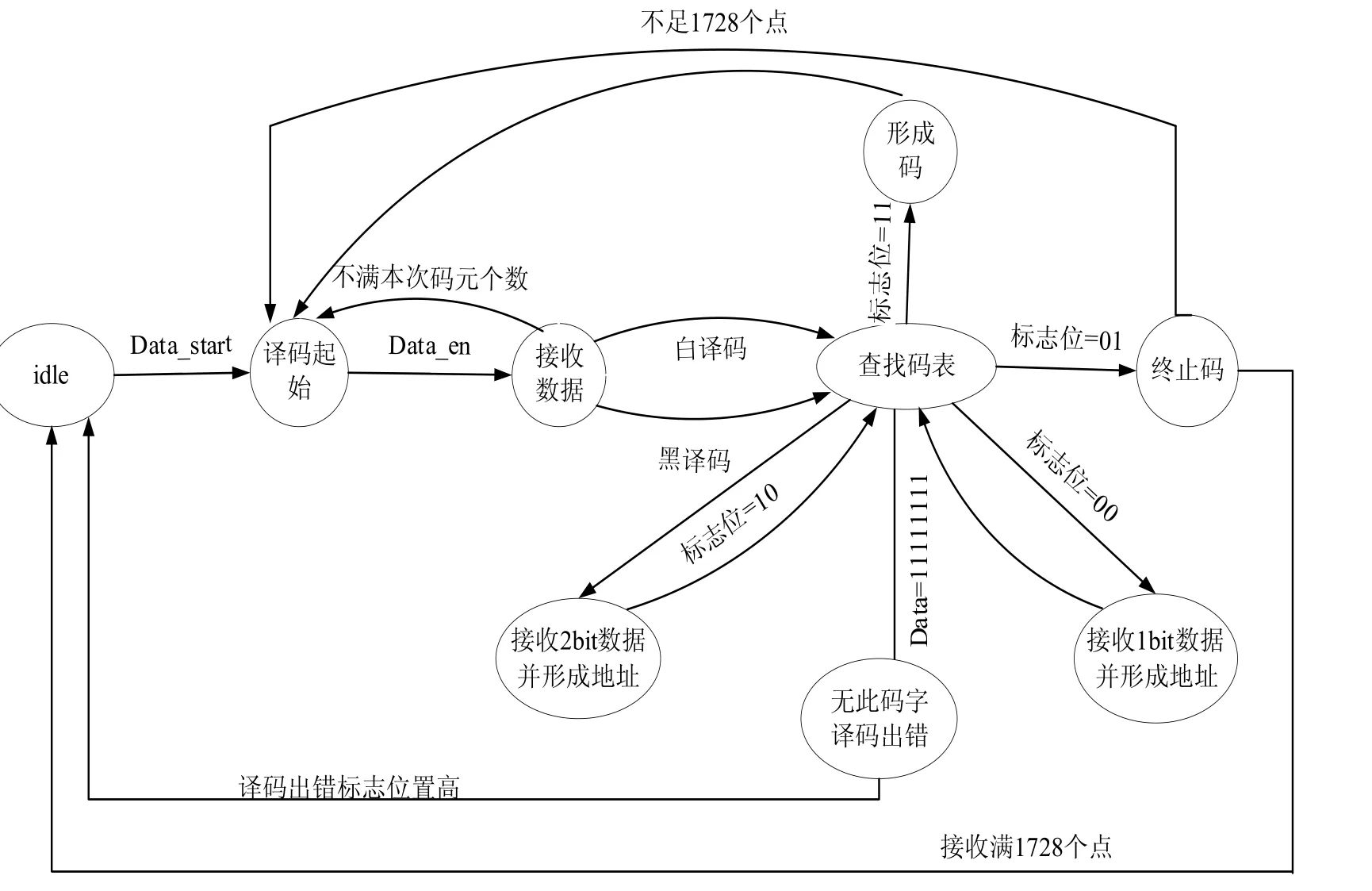

译码模块是传真译码电路的部分,对接收的串行数据译码。先检测EOL行同步标识,当确认EOL后,再对码元进行译码。白码字和黑码字进行译码是不同的,对应于两个不同的译码表。当译白码字时(对于每行第一个码元数据必须为白码字),首先接收4 bit数据,形成8 bit地址,根据这个地址查找白译码表存储空间并返回一个8 bit数据,判断这组数据的最低两位标志位的值来执行下一步操作。

当最低两位为‘00’时,再接收一位数据后和 data_8相加并形成新地址,再查找译码表;当最低两位为‘10’时,表示连续接收2 bit数据,和data_8相加,形成新地址,再查找译码表,依次重复执行操作,直到译出该码字或译码出错。当data_8的最低两位为‘01’时,输出数据高6 bit的值,并输出终止码数据有效使能信号;当data_8的最低两位为‘11’时,输出数据高6 bit的值,并输出形成码数据有效使能信号。

黑译码时,其译码过程和白译码基本相同。不同之处在于:首先接收2 bit码元数据,形成8 bit地址,根据这个地址来查找黑码表中对应的数据,再判断数据的标志位,执行相应操作。直至译出码字或译码出错。译码过程中先检测EOL序列,之后执行白译码、黑译码,白译码交替译码操作。对于该过程采用有限状态机来描述实现,见图2。

游程转换模块完成对译码输出的6 bit数据转换,串行输出该码字对应的连续黑点或连续白点的个数。当终止码数据使能有效时,把对应的6 bit数据进行转换,串行输出连续的“1”或“0”;当形成码数据使能有效时,6 bit数据表示有多少个64个连续的表示黑点或白点的“1”或“0”,最多连续输出1728个点。每1个点的输出需要一个时钟周期。例如,当本次白译码时,终止码对应的6 bit数据为“001000”,则输出连续8个“0”序列;黑译码时就输出连续的“1”序列,并输出数据有效使能信号。

行数据打印缓冲区负责接收“0”或“1”序列,由系统时钟打入由一个FIFO缓冲区,大小设定为存储两行的数据。当存储数据满一行时,串行输出到打印头打印。整个译码电路采用异步复位和全局同步时钟设计,时钟频率为50 MHz。两个码表的设计由ROM单元的IP核定制生成,只输入构造的码表数据。在QuartusII开发环境中采用Verilog HDL硬件语言描述电路设计。

图 2 译码状态

3 仿真验证与系统测试

该电路在QuartusII环境下进行功能仿真验证[5]。由于码表数据的生成采用软件方案实现并进行过软件测试,所以功能仿真主要对各种码元类型的组合情况和译码状态进行验证,并查看输出波形图,结果均与设计要求一致。

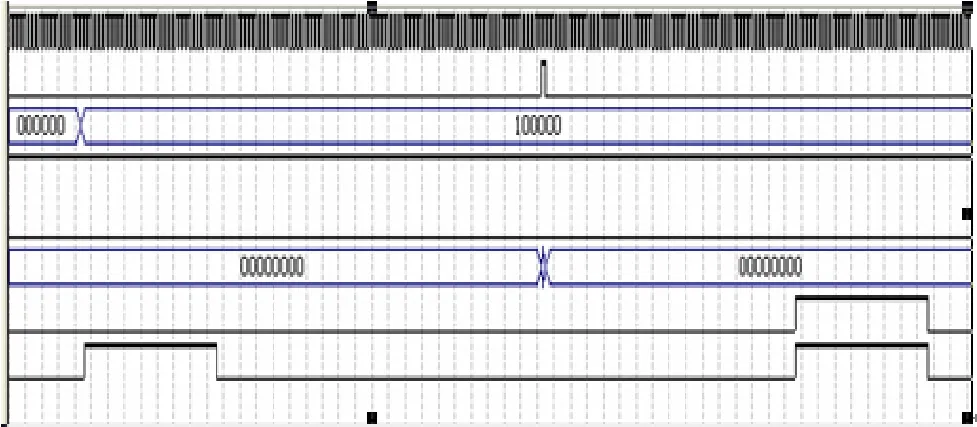

对于连续32个白点和黑点的编码数据,先进行白译码,连续32个时钟周期输出出‘0’数据和数据有效标识,下次输入表示32个黑点的编码数据,译出数据为连续32个‘1’,图3为仿真结果。

图3 仿真部分波形

针对Cyclone的FPGA器件库,综合该译码电路,时序报告满足设计要求,面积报告显示仅使用了 300多个LE(Logic Element)和6000多Memory bits。把综合后生成的网表文件、延时文件和FPGA器件库放到Modelsim环境中进行时序仿真,仿真结果与功能仿真一致,满足设计要求。

最后,在QuartusII环境下,通过SOPC配置CPU核,把该电路当做 CPU的外围模块,下载到 ALTERA 公司的Cyclone 系列器件 EP1C20F400C7开发板上。CPU核与该电路模块通过PIO端口连接,在NiosII开发环境中使用软件测试该电路系统。CPU核向电路写入数据和使能信号,待输出标识位数据有效后,再读出译码后数据。测试结果表明,对写入正确的编码数据都能读出正确译码结果;对异常的编码能正确处理,读出结果和预期一致,电路连续译码工作正常。

4 结语

本文通过对传真译码原理深入分析,结合FPGA的特点提出一种新的MHC码表构造方法,并在QuartusII开发环境下设计实现了传真译码电路。仿真测试结果表明该电路工作稳定,译码速度快并且占用很少的资源。与早期的传真译码电路设计相比集成度和工作频率更高;与目前的传真芯片相比,易于添加传真机的硬件功能,缩短开发周期,前景广阔。

[1] International Telecommunication Union,T.4(200),Standardization of Group 3 facsimile terminals for document transmission[S].Switzerland Geneva:3-11.

[2] 刘立柱.数字传真通信[M].成都:电子科技大学出版社,2000:169-171.

[3] 刘立柱.传真图像和传真信号处理原理与技术[M].北京:国防工业出版社,2006:58-66.

[4] 刘意先,韩俊刚,支亚军.基于 MHC快速译码算法的译码树的构造方法[J].通信技术,2009,42(07):28-30.

[5] 魏建英,叶玉堂,吴云峰,等.基于FPGA的超长CIS图像采集系统[J].通信技术,2009,42(02):298-300.